基于PXI总线的宽带频率计设计

功能的片内FIFO等优点,避免了自行设计PXI总线将大量的人力和物力投入到纷繁的逻辑验证、时序分析工作上,开发周期长的弊端。

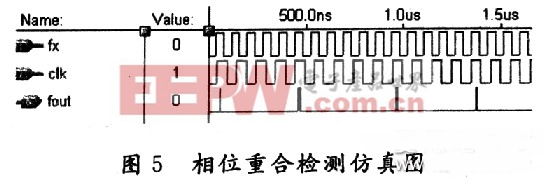

2.4 基于FPGA的相位重合检测电路设计

相位重合检测电路基本原理:利用FPGA内部的延时特性,信号经过方向延时后和原信号相与,即可获得与延时时间长度相同的输出,且输出间隔为各自的周期,当两路信号在第一次与门之后重合时,y输出高电平,此时判断两信号相位重合。EPM7032SLCA4-5的延时时间为5 ns。电路图如图4所示,时序图如图5所示。

3 基于PXI总线的宽带频率计设计

3.1 PXI总线介绍

PXI总线是在PCI总线内核技术上增加了成熟的技术规范和要求形成的。它通过增加用于多板同步的触发总线和参考时钟(10 MHz),用于进行精确定时的星型触发纵向,以及用于相邻模块间高速通信的局部总线来满足用户试验和测量的要求。PXI将Windows 95和Windows NT定义为其标准软件框架,并要求所有的仪器模块都带有按VISA规范编写的WIN32设备驱动程序,使PXI成为一种系统级的规范,确保系统易于集成和使用。

3.2 频率计系统组成

被被测信号经过调理电路预处理后与标准频率一起输出到相位检测电路后,由总线控制打开预制闸门,当检测到相位重合时,实际闸门开启并计数,当预制闸门下降沿到来时并不立即停止计数,而是等到下一次的脉冲重合点到来时关闭闸门并停止计数,系统由PXI总线进行控制。原理图如图6所示。

4 结语

介绍了一种基于PXI总线的高精度宽带频率计,采用预分频和相位同步测频相结合的技术,实现了宽带范围内的高精度测频要求,同时,通过FPGA将关键电路部分以逻辑编程的方式集成在芯片中,易于修改,使用方便。整个系统由PXI总线进行通信和控制,该频率计在电子测量领域有着广泛的应用前景。

- 基于虚拟仪器技术的短波电台自动测试系统(10-23)

- ATE开放式体系结构的硬件基础(10-30)

- 基于PXI的便携式测控系统(10-30)

- LXI 1.0 规范简介(02-27)

- 建立使用PXI、VXI和LXI的混合型测试系统(02-27)

- 关于网络时代的测试新技术(03-16)