智能温室环境测控系统专用CPU设计

个Compn(比较器组、n为可扩充)、一个Controller(控制单元)、一个AddrReg(地址寄存器)和八个.Reg0…Reg7(16位寄存器组),它们共用一组16位的三态数据总线。其工作流程和通用CPU相同,不同的专用寄存器保存指定的内容,指令的执行分顺序和转移两种方式。

该结构中有专门针对于智能温室测控系统而设计的一个浮点运算器和n个Comparray比较器。一方面由于本智能温室环境测控系统的一个很重要的功能就是硬件实现智能控制方法,同时运算模块主要对由采集模块所采集的环境因子进行比较分析和处理,而所采集数据通常是浮点数,所以本文在CPU的运算单元中增加了单独的浮点运算器;另一方面因为在智能温室测控系统中要随时对温度、湿度、CO2浓度等数据与作物生长的最佳值比较,如果数值超越了警戒线,就要采取措施。为了提高处理速度,方便比较,该结构中放置了比较器组,会把最常用的值在不同的比较器中固化,不但节省了取操作数的环节,而且也节省了时间。

2.2 比较寄存器组的设计

Comparray比较寄存器组是专门针对于智能温室测控系统设计的。在智能温室测控系统中要随时对温度、湿度、CO2浓度等参数与作物最佳生长值比较,如果数值超越了设定值,就要采取措施。该结构中放置了多个比较器,主要是为了方便比较,因此会把经过时间测试或专家提供的最常用的作物生长不同阶段的标准值在不同的比较器中进行固化,这样减少了取操作数的环节,自然就节约了时间。比较寄存器组的结构如图2所示。

在这个比较器组中只列了3个比较器,分别比较CO2浓度、湿度、温度,在智能温室控制系统中还有,光照强度、PH值、EC值、室外气象值、光合作用等,这里只是用这3个值作为示例。Comparray就相当与一个选择器,来分别选择比较寄存器组中的寄存器,这里设置了3个比较寄存器,当然也可根据需要进行增减。

3 浮点运算器的设计与仿真

本专用CPU设置浮点运算器的目的是要将智能控制算法在CPU内集成。而此浮点单元在进行复杂的算术逻辑运算时,主要设置了状态机,通过状态机对浮点运算单元的各个子模块进行调用,从而实现运算。本浮点运算单元的子模块主要有:加减法运算器、乘法运算器和除法运算器。它们之间的协调与配合是在总控状态机的负责下进行的,总控制状态机首先根据情况启动各个运算子模块使其进入运算状态,当运算结束后总控状态机会收到运算结束的反馈信号,并且将结果存入指定寄存器中,或用于输出或用于下一次运算。下面对各个子模块进行分别设计:

3.1 加减法器的设计与仿真

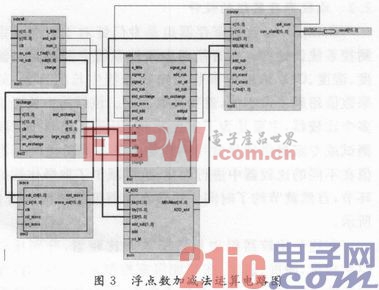

浮点加减法运算模块电路原理如图3所示。主要由6个模块构成,分别是Subcell模块、exchange模块、move模块、M_add模块、standar模块、cntrl模块。

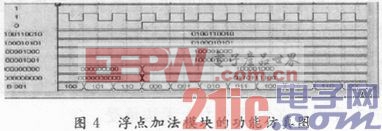

功能仿真如图4所示。

3.2 浮点乘法器的设计与仿真

浮点数乘法器的基本思想是符号与数值分开处理,2个操作数符号的异或为结果的符号,对于数值的处理采用的是取底数相乘、指数相加减的方法,然后对结果进行规格化处理后,再调整指数。按照浮点数的乘法步骤解释程序如下:

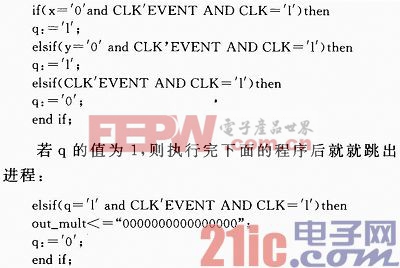

(1)零操作数判断

如果两个操作数中只要有一个操作数是0,则结果为0:

若q的值为0,则程序就继续执行一下操作。

(2)运算结果符号位判断

运算结果符号位主要是由两个操作数的符号决定,而其实现主要是通过一个异或门电路得到,程序如下:

(3)幂相加和尾数相乘

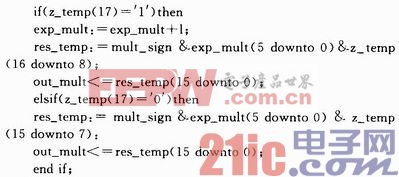

(4)规格化与舍入处理

当以上3步运算结束后,要对最高位进行判断,从而决定是否需要进行规格化,采用直接舍入法进行处理。

浮点乘法运算的功能仿真如图5所示。

3.3 浮点除法器的设计

除法器的VHDL核心处理代码如下:

功能仿真如图6所示。

针对温室环境控制的功能特点,在CPU中设计了可扩充的环境值比较器组。用来对采集的单个环境值与标准值进行比较,不但节省了存取数据的时间,也提高了温室环境测控系统的系统效率;单独设置了浮点运算器使得此专用CPU可以对智能控制算法的硬件集成提供良好的支撑,使得无PC的参与、无庞大专家数据库系统的支撑,同样具有反应专家知识的功能。

- SoC的发展将使测试与测量设备嵌入芯片(10-21)

- 网络系统方案的可靠性测试 (04-25)

- 网络协议一致性测试平台设计(07-09)

- 基于虚拟仪器的运动位移测量系统的实现(07-26)

- 基于USB接口的电化学沉积仪器数据采集系统的研究(11-13)

- 新型数字化故障录波器方案(01-07)