超声波随钻井径检测仪的数据采集与传输

摘要:为了更好地发挥随钻测井仪检测数据的真实性和使用灵活性等优点,文中基于Actel公司的APA075FPGA数据采集和传输系统所涉及到的AD数据采集、FPGA数据缓存、FPGA中数据的串口发送三部分,在实验室自制的一块FPGA最小系统板上,开发了一种激发换能器来对回波进行采集、缓存和传输。

关键词:随钻井径检测;AD数据采集;FPGA;串口发送

0 引言

在油、气开发过程中,测井是必不可少的。在开发初期,有勘探测井,在开发中后期,则有生产测井。传统的电缆测井存在着种种难以解决的问题,如在某些大斜度井或特殊地质环境(膨胀粘土或高压地层)钻井时,电缆测井就无法进行。除此之外,电缆测井是在钻井完成之后,用电缆将仪器放入井中进行测量,钻井过程中带出的钻碎的岩屑和钻井液会侵入地层,这样测量的数据与真实的数据有一定的差别。因此,随钻测井技术就应运而生,而无论是在电缆测井还是随钻测井中,数据采集和传输都是必不可少的。

本文所涉及的超声波随钻测井径的基本原理是:沿着油井的径向向井壁垂直发射超声波,当发出的超声波遇到井壁时发生反射,反射的回波被换能器接收。这样,根据超声换能器发出超声波到反射回波被换能器接收所经历的时间t和已知的超声波在泥浆中的速度v就可以计算井径的长度。本文运用AD对回波进行采集,运用FPGA对AD转换后的数据进行缓存和传输,FPGA为AD提供片选信号和转换时钟,转换之后的数字量再给FPGA进行串转并、FIFO存储、串口发送。在本文中,FPGA采用的是Actel公司的APA075,开发平台采用的是Liber08.5。

1 系统的总体设计

本系统的总体设计思想是:FPGA为AD提供片选及时钟等控制信号,AD将数字化后的数据送给FPGA,并在FPGA中进行串并转换、缓存等一系列数据处理后,再通过MAX232完成TTL电平到RS-232电平的转换,然后在PC机上运用串口调试小助手显示数据。通过分析串口调试小助手上显示的数据来判断是否正确,从而验证系统设计的合理性。其系统框图如图1所示。

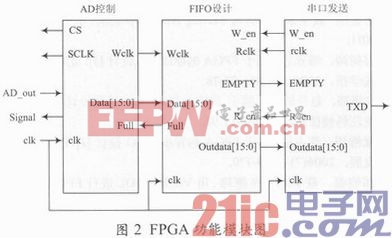

在本系统中,FPGA的功能模块主要包括AD控制模块、FIFO设计模块和串口数据发送模块三部分。FPGA系统与外围电路的信息交换主要由AD_out、clk、SCLK、CS、TXD等信号线完成。其中,AD_out负责将AD转换后的数字信号送入FPGA;CS和SCLK是FPGA为AD提供的片选信号和时钟信号,用来控制AD的转换;TXD是FPGA输出数据的通道:clk是FPGA的时钟信号。系统时钟采用50 MHz,其FPGA功能模块电路框图如图2所示。

2.1 AD控制模块的设计与实现

AD控制模块要实现的功能是提供AD转换的片选信号和AD转换时钟,以及FIFO的写时钟、FIFO要存储的16位并行数据,接收AD转换的串行数据并实现串转并,同时提供换能器的激励信号。本设计中,AD转换芯片采用的是ADI公司的12位AD7352,该芯片具有耐高温、功耗低等优点。片选信号CS的周期决定了AD采样的速率,FPGA为AD提供的转换时钟SCLK的频率大小决定了AD的转换时间,正常工作时,完成一个数据的转换至少需要14个时钟下降沿。在本设计中,综合考虑各方面的因素,AD采样频率设计为2.5 MHz,完成一个模拟量的转换采用18个转换时钟,这样,AD的转换时钟SCLK的频率为45 MHz,该时钟由FPGA中锁相环对50 MHz的系统时钟分频得到。片选信号CS高低电平的控制采用计数器对与转换时钟相同的时钟计数来实现,每当该时钟的上升沿到来时,计数器加1,计数器加到17后,又从零开始循环计数,当计数器的值小于14时,将片选信号CS置低,否则置高。片选信号与转换时钟的时序如图3所示。

在本部分设计中,考虑到实际应用中需要对四个换能器接收的数据进行采集,为了区别各个换能器的数据,设计时在串转并的过程中人为添加了四位数据作为标志位。为了使AD的采样率、FPGA中串转并的速率以及FIFO的写速率保持一致,FIFO的写时钟采用一个计数器对AD的转换时钟计数获得。每当转换时钟SCLK的下降沿到来时计数器加1,计数器从零到13循环计数,计数器每循环一个周期就提供一个写时钟上升沿(写时钟上升沿有效),使FIFO完成一次写操作。在AD正常工作时,第一个时钟下降沿会输出两个前导零,然后从第二个时钟下降沿开始依次从高位到低位输出12位有效的数据,并在第13个下降沿完成最后一位数据的输出,最后在之后的上升沿返回跟踪模式。因此,在串转并时,要从第二个时钟下降沿开始。

2.2 FIFO的设计与实现

FIFO的主要功能是实现不同时钟域之间的数据传输。FIFO分为同步FIFO和异步FIFO,本设计中采用的是异步FIFO,涉及到的主要参数包括FIFO的深度,FIFO的读、写时钟,FIFO存储的数据的宽度和读、写指针等。考虑到AD采样速率为2.5 MHz,每次开始转换后持续的时间大约为600 μs,因此,FIFO需要缓存的数据大约为1 500个,Actel公司的APA075中有12个256X9的RAM空间,最多能缓存1 536个16位的数据。

为了保险起见,FIFO的深度设计成1 536,根据实际应用的需求,FIFO的宽度设计成16位,写时钟频率和AD采样频率保持一致,读时钟频率和串口传输速率保持一致。同时,为了防止数据溢出或读取无效的数据,FIFO的设计采用了空满标志位。当FIFO写满时,满标志位置1,禁止继续向FIFO中写入数据:当FIFO为空时,禁止从FIFO中继续读取数据。空满标志的准确判断是FIFO设计的一大难点,本设计中采用了列举的算法实现空满标志的判断。FIFO写满有以下两种情况:第一,写指针加1等于读指针,并且写使能有效,再继续写操作时,FIFO就为满,满标志位置1;第二,写指针加1等于FIFO的深度并且读指针为零,再继续写操作时,FIFO就为满,满标志位置1。与满标志情况类似,FIFO读空也有以下两种情况:第一,读指针加1等于写指针,再继续读操作时,FIFO就为空,空标志位置1;第二,读指针加1等于FIFO的深度并且写指针为零,再继续读操作时,FIFO就为空,这时,空标志位置1。

2. 3 串口发送的设计与实现

串口发送模块负责把处理后的数据从FIFO中读出,将其按通信协议传送给MAX232完成电平转换后送给PC机。发送数据采用的波特率是9 600,数据帧格式如图4所示。

- 超声波测距器的设计(10-30)

- 基于DSP的双频超声波流量计硬件电路设计(04-23)

- 超声波流量计传感器线缆的加长和剪切(10-14)

- TDC-GP21完美适合超声波热量表的解决方案(02-28)

- 一种原油超声波相关流量计的设计(04-25)

- 基于P89LPC932超声波测距仪(07-09)