基于硬件协议栈的以太网远程数据传输系统

摘要:本文介绍了一款单片网络接口芯片W5100,该芯片内部集成了TCP/IP硬件协议栈,支持多种网络协议。给出了基于STM32处理器的硬件电路连接图和软件程序设计。目前,该系统已成功应用在多个建筑能耗监测项目中,运行结果表明该系统通信稳定可靠,能够满足项目对远程数据传输的需求。

关键词:以太网;数据传输;硬件协议栈;STM32

引言

数据采集与传输系统一直是工业控制、环境参数监测、建筑能耗信息监测等多个领域共同关注的问题,尤其是针对远程数据传输问题。受传输距离的限制,传统的现场总线通信方式只适合于近距离的数据传输;而基于GPRS技术的数据传输系统虽然可以不受距离的限制,但其按照流量进行收费,对于大量数据连续传输而言资费不低,在实际的项目中应用也不是很广泛。目前,基于以太网的数据传输系统以其成本低廉、通信速率高和支持远距离通信等诸多优点,在监测领域得到了越来越多的应用。

常见的网络驱动芯片有RTL8019、CS8900、ENC28J60、DM9000、W5100等,其中ENC28J60支持串行SPI接口通信方式,接口电路设计相对简单。RTL8019、CS8900和DM9000都是并行总线式驱动方式,需要连接较多的数据线、地址线以及读写控制引脚等。W5100既支持串行SPI接口,同时也支持并行总线方式。这几款芯片中除了W5100内置TCP/IP协议栈之外,其余都需要用户自己开发以太网驱动程序,需要占据大量的存储空间以及宝贵的RAM内存单元;而且,软件的实现方式与硬件集成相比,稳定性和可靠性也稍差。

1 W5100芯片介绍

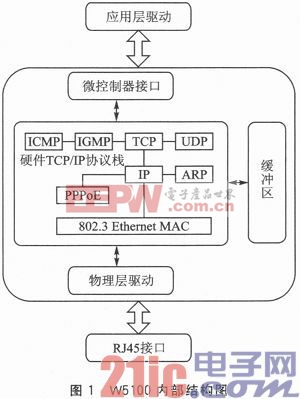

W5100是韩国Wiznet公司生产的一款多功能的单片网络接口芯片,内部集成有10/100M以太网控制器,且经过多年实际项目应用验证的硬件TCP/IP协议栈,提供全双工以太网解决方案。与该公司之前的产品W3100相比,W5100内部集成了物理层RTL8201CP核,它是一款集TCP /IP协议栈、以太网MAC和PHY为一体的网络接口芯片,具有更高的集成度和更稳定的工作性能,便于硬件实现。W5100芯片同时支持直接并行总线、间接并行总线和SPI串行总线共3种接口方式与主控芯片进行通信,可以满足不同场合的需求。这些性能使得用户不需要考虑以太网TCP/IP协议栈的移植等复杂的软件驱动程序,可以像访问外部存储器一样操作W5100,实现网络通信功能。W5100的性能特点如下:

①内嵌10/100BaseT以太网物理层;

②理论最大传输率可达25 Mb/s;

③支持自动MDI/MDIX,自动校正信号极性;

④支持ADSL连接(支持PPPoE协议中的PAD/CHAP认证模式);

⑤支持4个独立端口同时运行;

⑥内置16 KB存储器用于数据发送/接收缓存。

1.1 内部结构及引脚功能

如图1所示,W5100将网络协议的处理分成一个由特定处理器执行的控制部分和一个硬件线路部分,实现硬件化的TCP、UDP、ICMP、IPv 4、ARP、IGMP以及PPPoE协议,含有连接以太网协议中的数据控制及MAC协议;按照功能可以将W5100的引脚分为与处理器接口的通信引脚、以太网物理层功能引脚、时钟引脚、LED工作状态指示引脚、电源引脚等几类。直接总线接口方式需要用到ADDR[0~14]共15个引脚;而间接总线接口方式只需要用到地址线0和地址线1,其余的地址线ADDR[2~14]通过电阻接地即可;使用SPI接口方式时需要注意,必须将SEN引脚接高电平,才能使SPI功能有效,后面在硬件电路部分介绍。

1.2 寄存器功能介绍

W5100的寄存器可以分为通用寄存器和端口寄存器两类。其中,通用寄存器包括对W5100的网络配置、中断、超时参数以及缓冲区大小等设置;端口寄存器是针对W5100的4个独立的端口设置,包括端口模式寄存器、端口命令寄存器、端口中断寄存器和端口状态寄存器等在内的共17个寄存器。

通用寄存器的详细信息如表1所列。针对中断寄存器IR共有7个中断源,当任何一个未被屏蔽的中断置为高电平时,W5100的中断输出引脚INT将会一直保持低电平,MCU通过读取IR寄存器定位中断源,并进行中断程序处理,之后清零IR中相应的位,INT引脚才恢复为高电平。

W5100内部共有16 KB发送/接收缓冲区,发送和接收各占8 KB,默认每个端口的发送和接收均为2 KB,即RMSR=TMSR=0x55,在实际使用过程中,用户可以根据实际情况调整发送/接收缓冲区大小。如图2所示,通过修改每个端口对应的S1和S0寄存器可以修改相应的端口缓冲区大小。

端口寄存器是分别针对4个独立Socket的寄存器,以Sn_xx的形式表示,其中n取值为0、1、2、3。端口模式寄存器Sn_MR定义了该端口工作在TCP模式或者是UDP模式,不同模式下端口寄存器的表现形式不一,本文对此不作过多的阐述。

2 系统方案设计

本文核心处理器采用的是STM32F103VET6,它是一款基于Cortex—M3内核的ARM处理器芯片,内部集成了512K Flash程序存储空间和64K的SRAM数据存储空间。STM32F103VET6最高工作频率72 MHz,含有资源外设接口,包括2个12位数/模转换器、7个定时器、CAN总线接口、SPI通信接口、3路USART串行通信接口等资源。图3展示了基于STM32F103VET6的W5100通信系统结构图,包括电源电路、时钟电路、复位电路、

JTAG调试电路和W5100以太网通信电路。

- 使用NILabVIEW软件和PXI硬件完成飞机喷流噪声测量(05-12)

- 使用LabVIEW软件和NI PXI硬件为并网光伏(PV)设备快速开发监测系统(07-08)

- 选择硬件在环(HIL)测试系统I/O接口(06-12)

- 基于LabVIEW的航天执行器的软硬件测试(09-25)

- 一种数字示波器的微处理器硬件设计(09-08)

- N2X与IXIA硬件平台融合方案(11-14)