计算ADC噪声系数的注意事项

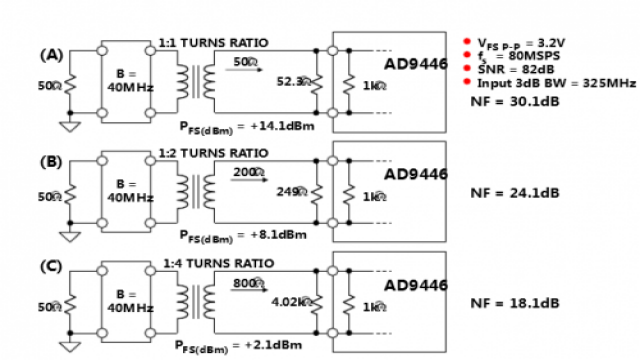

6C中的变压器匝数比为1:4。AD9446输入端与一个4.02 kΩ电阻并联,使得净输入阻抗为800 Ω。噪声系数又降低6 dB。理论上,匝数比越高,则改善幅度越大,但由于带宽和失真限制,更高匝数比的变压器一般并不可行。

图6:利用RF变压器改善ADC整体噪声系数

级联噪声系数

即使采用匝数比为1:4的变压器,AD9446的整体噪声系数也有18.1 dB,按照RF标准,这一数值仍然较高。应当注意,AD9446 ADC的82 dB SNR代表了出色的噪声性能,系统应用的解决办法是在ADC之前提供低噪声高增益级。在一个典型接收机中,ADC之前至少有一个低噪声放大器(LNA)和 混频级,它能提供足够高的信号增益,从而将ADC对系统整体噪声系数的影响降至最低。

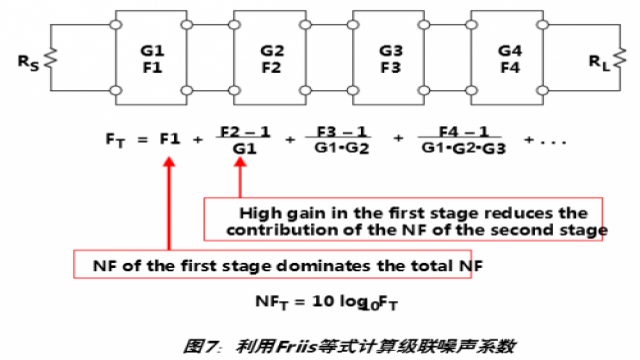

这可以通过图7来说明,其中显示了如何利用Friis等式来计算级联增益级的噪声因数。注意,第一级的高增益降低了第二级噪声因数的影响,因此第一级的噪声因数在整体噪声系数中占主导地位。

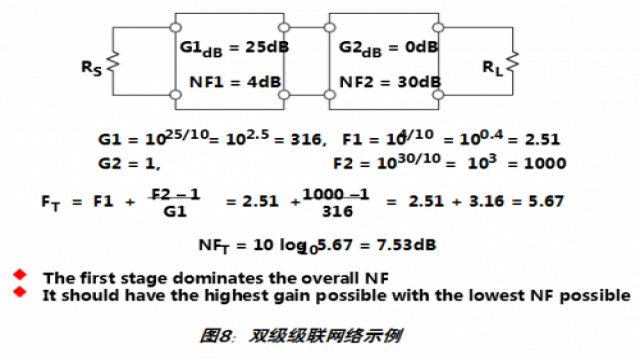

图8显示了置于一个相对较高NF级(30 dB)之前的一个高增益(25 dB)低噪声(NF = 4 dB)级的影响,第二级的噪声系数是高性能ADC的典型噪声系数。整体噪声系数为7.53 dB,仅比第一级噪声系数(4 dB)高3.53 dB。

结束语

应用噪声系数概念来表征宽带ADC时,必须特别小心,防止得出令人误解的结果。试图简单地通过改变等式中的值来降低噪声系数可能会适得其反,导致电路总噪声提高。

例 如,根据以上等式,NF随着源电阻的增加而降低,但增加源电阻会提高电路噪声。另一个例子与ADC的输入带宽B有关。根据等式,提高B会降低NF,但这显 然是相互矛盾的,因为提高ADC输入带宽实际上会提高有效输入噪声。在以上两个例子中,电路总噪声提高,但NF降低。NF降低的原因是源电阻或带宽提高 时,信号源噪声占总噪声中的较大部分。然而,总噪声保持相对稳定,因为ADC引起的噪声远大于信号源噪声。因此,根据等式,NF降低,但实际电路噪声提 高。

有鉴于此,当处理ADC时,必须小心处理NF。利用本文中的等式可以获得有效的结果,但如果不全面理解其中涉及到的噪声原理,这些等式可能会令人误解。从 孤立的角度看,即使是低噪声ADC,其噪声系数也会相对高于LNA或混频器等其它RF器件。然而,在实际的系统应用中,ADC前方至少会放置一个低噪声增 益模块,根据Friis等式(见图8),它会把ADC的总噪声贡献降至非常低的水平。

- 无线通讯的噪声干扰与验证要点(07-11)

- 通过改变电源开关频率来降低EMI干扰(05-05)

- 无线基站接收通道混频器的设计选择(07-05)

- 基站射频卡时钟树设计问题(05-03)

- 基于频谱分析来的RF功率和寄生噪声辐射限制(07-25)

- 安捷伦保持业界50GHz最高噪声测量精度(12-10)