资深老工程师分享:利用PSpice仿真数字滤波器的快速简单方法

PSpice 已经成为模拟电路仿真使用的行业标准工具。模拟电路具有真实的物理实现,可以用它们的原理示意图进行仿真,其频率响应是电路时间常数的结果。与之相反的 是,数字滤波器对一系列样本进行数学运算。数字滤波器的时间常数隐藏在采样间隔T中。因此数字滤波器一般是通过它们的传递函数进行数学仿真,而且为了做到 这一点,能够方便地仿真由采样率fs引起的采样延时T=1/fs非常重要,因为这个延时定义和衡量了整个滤波器的响应性能。

通常拉普拉斯变换用于模拟电路的行为建模,因为它将时域变换成为复频率s域。数字滤波器的频率响应作为一个特殊例子,可以从拉普拉斯变换的时移理论(延时理论)推导出来。该理论表示,如果时间函数f(t)在时域中被延时了时间T,那么在频域中的结果要乘以e-sT,见公式(1)。

![]()

esT项经常被称为延时因子,如果用符号z代替,如公式(2)所示,那么拉普拉斯变换将升级为所谓的z变换。这样,回到时域,z-n对应延时的nth样本,z0是当前样本,zn代表未来的nth样本。

![]()

本 设计实例介绍了一种在PSpice中进行数字滤波器频率响应仿真的快速简单直观方法。PSpice模拟行为建模符号库abm.slb包含LAPLACE部 分(拉普拉斯电压控制的电压源),其中任何s域传递函数都可以用分子(NUM)和分母(DENOM)的形式写出来。为了仿真z域传递函数,首先要在电路参 数列表中定义采样间隔T。然后用公式(2)代替zn,在LAPLACE部分写出z域传递函数。在PSpice中,这种替代可以通过定义一个函数(公式(3))完成,而这个函数就是本设计实例的核心。

![]()

举例来说,如果用分子或分母形式将z(-10)写下来,PSpice将用e-10sT替代z(-10) (s是LAPLACE部分使用的拉普拉斯变量)。公式(3)可以放在包含文件中,或更方便地放在新原理图模板FUNCTIONS中。

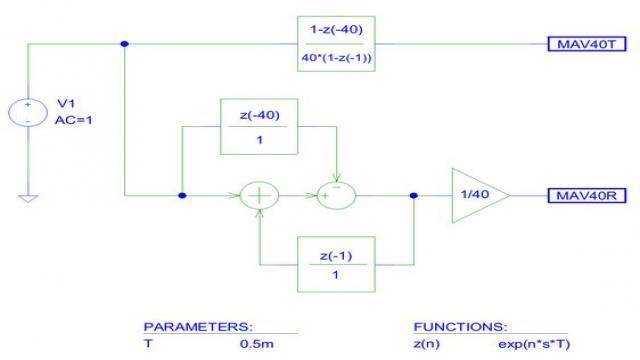

图1:交流线干扰平均器的PSpice原理图(梳状滤波器)。

图1显示了用于数字移动平均滤波器交流仿真的PSpice原理图。移动平均滤波器将拒绝频率在滤波器零点处的任何信号。

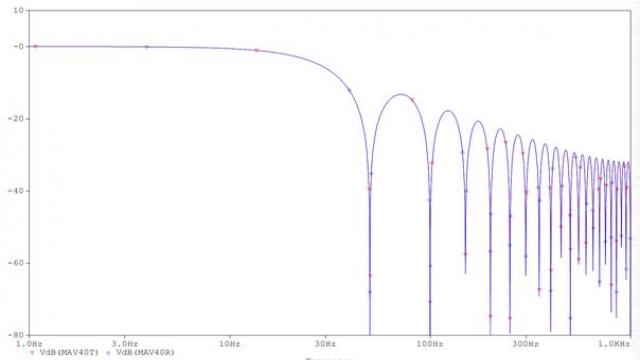

举例来说,假设采样频率fs = 2kHz或T = 0.5ms。为了抑制50Hz的电力线(PL)干扰,来自同一个周期的样本必须被平均处理。在2kHz采样率时,一个电力线周期由20ms/0.5ms = 40个样本组成。平均器可以用传递函数直接仿真(输出MAV40T),或借助接近于其实际算法实现的结构并利用延时模块、增益模块以及和差结点进行仿真 (输出MAV40R)。该仿真在电力线干扰的所有谐波处都有凹槽,如图2所示。

图2:平均器的频率响应。

上述方法既快又容易。我已经用了10年了,在发现参考1中的设计实例后深受启发,决定分享我的知识。参考文献2介绍了用上述方法仿真的其它数字滤波器例子。

- 三大原因为你解读网络监控系统延时问题(01-22)

- MIMO分布式天线系统中的延时失衡性能分析(08-29)

- 两种基于FPGA的软件滤波方法(07-22)

- 射频采样ADC输入保护:这不是魔法(07-27)

- 射频(RF)采样:数字混频器能使混频操作妙趣横生(11-02)

- 信号采样定理:三个条件只要满足两个(07-01)