为什么CPU时钟频率在过去5年里没有增加?

CPU时钟频率在过去5年里没有增加是很多不同类别的原因导致的。当设计一个CPU的微架构时,其中一个关键的设计决策就是如何实现更高的性能。在 奔腾4时代,英特尔选择了具有非常高的时钟频率和相对较窄的管道。这种方法有很多优点,其中之一就是它很容易加快单线程和串行代码。软件内并不需要操作很 多的并行指令,因此大多数软件会立刻见其好处。

一、功率

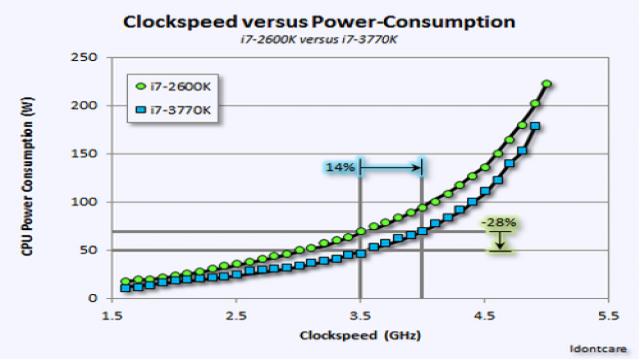

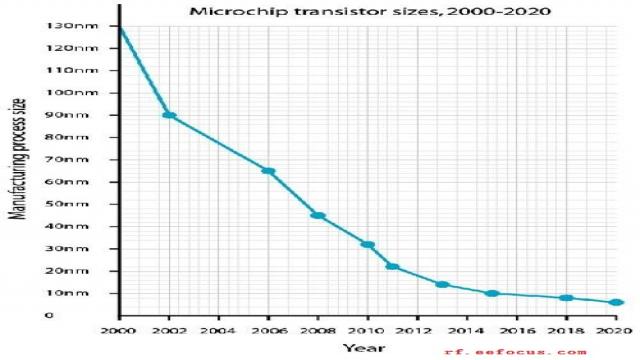

图为时钟频率与功耗的关系

然而,这种方法也有它的缺点,它忽略奔腾4本身的执行瑕疵。在这里,我们只讲概念本身的缺陷。主要是CPU的微架构一直与电墙冲突,并且,高频的微架构与很多已被发明出来用来处理功率问题的低功耗设计技术都不适合。此处,我将触及两个主要的低功耗设计方法。

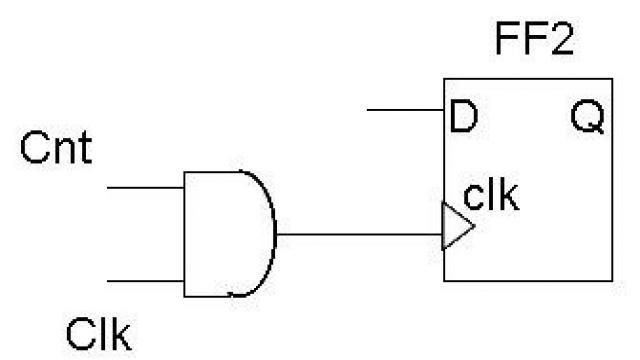

一个是时钟门控技术,时钟门控技术会在每个状态元件(寄存器、锁等)之前插入一个时钟启动系统,以至于如果没有新的数据写入的话,元件将没有时钟控制。 这样就可以节省大量因回写相同的高速缓存而浪费的充电/放电时间。这个方式也将一个附加延迟(门控功能)插入时钟路径。高频率的设计一般是低利润率运行, 根本就不适合在最关键的信号(时钟)插入附加可变延迟。

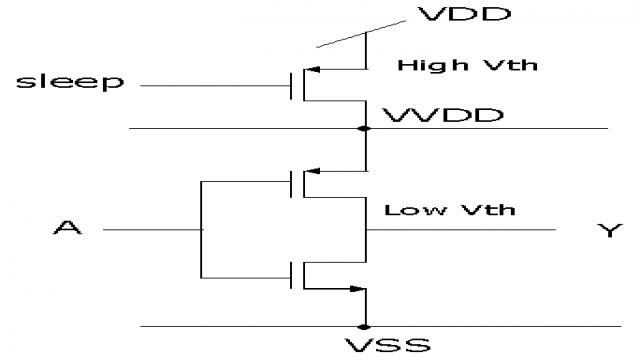

另一个常见的技巧是电源门控。这涉及到要在芯片不同部分的电压源上放上晶体管。通常情况下,当不使用时,那些不同的功能模块和供电部分会关闭,但高频设 计往往不会这样做。电源控制晶体管不但需要添加一个额外的压降,从而延缓晶体管开关速度,而且一个非常细的流水线处理器根本没有多少部分可以在任何给定的 时间内被关闭。

因此,从微架构的角度来看,高频和细的设计不只是智能power-wise。

二、晶体管缩放

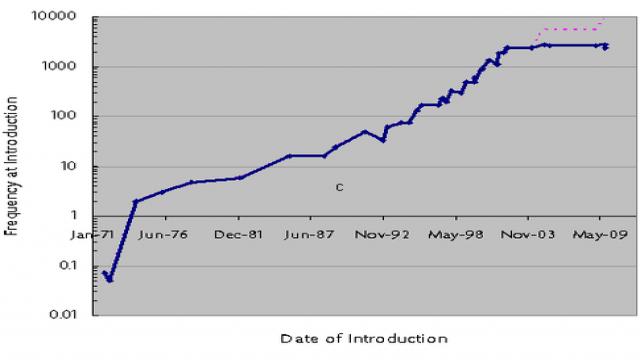

处理器频率没有上涨的另一个主要原因很简单,就是晶体管本身并没有变得更快。

其他人提到了晶体管宽度尺寸的因素,但晶体管宽实际上是稳步下降的,并且会继续下去,摩尔定律在这方面还是很好地发挥作用的。

英特尔目前正在45纳米的基础上制造32纳米的HKMG(high-k绝缘层+金属闸极) 。两年之前,它是65纳米,再之前是90纳米。TSMC, IBM and GlobalFoundries 公司今年开始生产28纳米芯片。英特尔正计划调整到22纳米。 (更新:14nm已经出来了)。

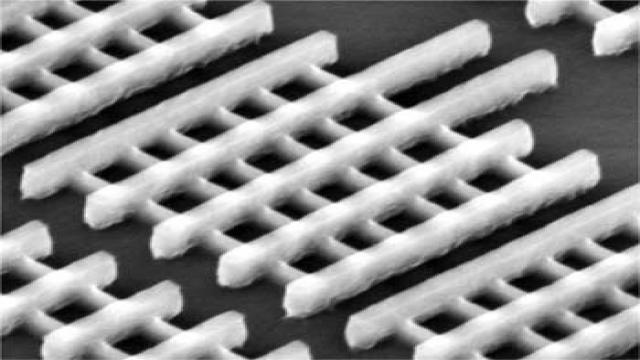

然而,问题是,当晶体管的尺寸越来越小时他们却没有越来越快。要理解这一点,有点MOSFET(金氧半场效晶体管)的背景是必要的。

众所周知,晶体管的开关速度取决于许多因素。其中一个主要因素是电场在闸极(控制到交换机)中创建的强度。电场强度取决于闸极(其变小,晶体管收缩)的两个区域,以及闸门厚度。

随着晶体管的缩小,门的面积在减少。在过去,闸极区域面积的减少意味着一个晶体管的闸极也可以做得更薄。如果你知道基本的电容器是如何工作的,你就 会知道,两个导电板之间距离越小,它们之间的电场就越强。这个工作原理在MOSFET上同样通用。更薄的闸极电介质导致有更强的电场通过晶体管沟道,这意 味着晶体管的切换速度更快。晶体管闸极面积减少意味着闸门可以做得更薄,并且对负载电容增加无害。

然而,至于45纳米,现在的闸介质约0.9纳米厚——大约一个二氧化硅分子的大小,所以根本不可能做出更薄的了。因此,英特尔改用以铪材料为基础材料的High-K取代二氧化硅,成为闸极电介质(许多人怀疑是硅酸铪)。他们还把连接闸门的材料从多晶硅变成金属材料。

这种方法有助于提高晶体管的速度,但它太昂贵了,只能是一个权宜之计。事情很简单,每一次我们利用之前已有的简单的缩放比例缩小晶体管,都会导致更快的晶体管结束。

三、芯片缩放

频率斜升放缓的另一个主要原因是晶体管不再是唯一的——在某些情况下,即使是最大的——处理器可以运行多快的关键。现在,连接这些晶体管的电线成为延迟的主要因素。

随着晶体管越来越小,连接它们的电线变得更细。细线意味着更高的阻力和更低的电流。事实是较小的晶体管能够驱动少量的电流,很容易发现,晶体管的开关速度只能部分确定电路的路径延迟情况。

当然,在芯片设计过程中可以使用许多技巧来对付这个问题。一个布局和布线良好的工程师将尝试以类似的路径来规划其时钟和数据信号的路线,这样可以使两个 信号同时传送,并在同一时间到达目的地。对于数据密集型芯片,轻控设计会是一种非常有效的解决方案,例如固定功能的视频编解码引擎或网络处理器。

然而,带有web交互的微处理器是一个非常复杂的、非常规的设计,数据访问多个地点时并不总是遵循时钟

- SDH微波传输中的同步时钟(01-06)

- 微波时钟同步解决方案(12-06)

- 基站射频卡时钟树设计问题(05-03)

- 微波时钟同步设计方案(12-10)

- DSP硬件设计的几个注意事项(06-04)

- 电压检测与接口电路设计原理图(06-23)