FinFET存储器的设计、测试 和修复方法

存储器测试始终要面临一系列特有的问题。现在,随着FinFET存储器的出现,需要克服更多的挑战。这份白皮书涵盖:

- FinFET存储器带来的新的设计复杂性、缺陷覆盖和良率挑战

- 怎样综合测试算法以检测和诊断FinFET存储器具体缺陷

- 如何通过内建自测试(BIST)基础架构与高效测试和维修能力的结合来帮助保证FinFET存储器的高良率

虽然这份白皮书以FinFET工艺(制程)为重点,但其中很多挑战并非针对特定制程。这里呈现的存储器测试的新问题跟所有存储器都有关,无论是Synopsys还是第三方IP供应商提供的或是内部设计的。

FinFET与平面工艺比较

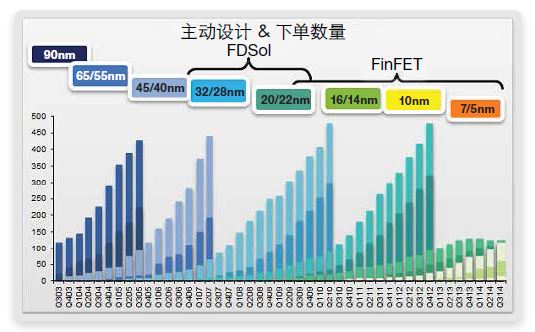

英特尔首先使用了22nm FinFET工艺,其他主要代工厂则在14/16nm及以下相继加入。自此,FinFET工艺的流行

性和重要性始终在增长。如图1所示。

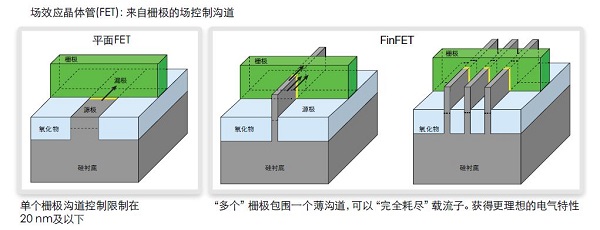

图1:90nm 到 7/5nm FinFET工艺节点下活跃设计及投片项目的增长 要理解FinFET架构,设计人员首先应与平面架构进行沟道对比,如图2所示。左图标识平面晶体管。改为FinFET的制程相关的主要动机是制程工程师所谓的“短沟道效应”和设计工程师所谓的“漏电”。当栅极下面的沟道太短且太深以至于栅极无法正常地控制它时,即使在其“关闭”的情况下,其仍然会局部“打开”而有漏电电流流动,造成极高的静态功率耗散。

中间这张图指示的是FinFET。鳍片(灰色)较薄,栅极将它周围完全裹住。鳍片穿过栅极的所有沟道部分充分受控,漏电很小。从工艺上说,这种沟道将载流子完全耗尽。这种架构一般使用多个鳍片(两个或三个),但未来工艺也可能使用更多鳍片。多鳍片的使用提供了比单鳍片更好的控制。

使用多鳍片突出了FinFET与平面架构之间的重大差异。平面工艺使用晶体管宽度和长度尺寸的二维界面。而在FinFET中,鳍片大小是固定不变的,栅极厚度(其定义了沟道长度)也是固定不变的。改变FinFET的唯一参数是鳍片数量,而且必须是整数。比如:不可能有2? (两个半)鳍片。

图2:平面架构与FinFET架构对比 FinFET降低了工作电压,提高了晶体管效率,对静态功耗(线性)和动态功耗(二次方)都有积极作用。可节省高达50%的功耗。性能也更高——在0.7V上,性能(吞吐量)比平面工艺高37%。

FinFET复杂性带来了制造困难

与平面工艺相比,FinFET的复杂性一般会导致更加昂贵的制造工艺,至少初期是这样。随着代工厂经验不断丰富和对工艺过程的控制越来越娴熟,这些成本可能会下降,但就目前而言,放弃平面工艺的话会增加成本。

FinFET还存在热挑战。由于鳍片直立,晶片的基体(衬底)起不到散热片的作用,这可能导致性能下降和老化。热挑战还会影响修复,因为在某些情况下,存储器不仅需要在生产测试中修复,以后还需要在现场修复。

在使该工艺投产、扩大到量产等情况下,代工厂必须考虑这些挑战。一般来说,代工厂还要负责存储器位单元,需要对其做全面分析(通过模拟)和鉴定(通过运行晶圆)。IP提供商,无论是存储器、标准单元还是接口提供商,也要在构建自己的布局的同时考虑这些问题。

SoC设计人员受到的影响不大,至少对于数字设计流程来说是这样。一般来说,设计人员见到鳍片的次数绝不会比他们以往见到晶体管的次数更多,除非他们想在其布局与布线工具所使用的,采用金属结构进行连接的标准单元内部一探究竟。

STAR存储器系统

Synopsys生态系统(图3)包括创建布局、完成提取、模拟等需要的所有工具。Synopsys内部各IP小组能够充分利用完整的Synopsys工具套件来设计、验证并测试Synopsys IP,包括存储器在内。

图3:Synopsys工具套件 Synopsys已经从最底层起搭建了自己的专门知识。他们与所有不同的FinFET厂家均构建了多个测试芯片:三星、TSMC、英特尔、GLOBALFOUNDRIES和UMC。截止2015年8月,Synopsys运行过的FinFET测试芯片有50个以上。这些芯片均使用了被称之为DesignWare?STAR存储器系统?的Synopsys测试和修复解决方案,其中STAR表示自测试与修复。

自测试和修复曾经在很多代工艺制程上使用过,不只是FinFET。通过不断投入,Synopsys改善了STAR存储器系统。图4中,STAR存储器系统用紫色方块指示。它们包含STAR存储器系统IP编译器生成的RTL模块以应对各种存储器:S

FinFET存储器修复方 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)