实现高速串行I/O效率的嵌入式测试

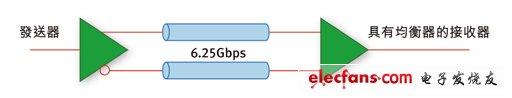

有一个讯号被接收机恢復了。

图1:高速串列链路测试的实际例子。

FGPA的用途

随着串列技术在嵌入式系统中的出现,FPGA将扮演一个重要的作用。长期以来FPGA都是嵌入式设计师使用的实现技术,而随着FPGA性价比的演进,其作用正增加。FPGA正日益增多地成为一个整合平台,它具有类似晶片上系统(SoC)的功能,而这些功能则利用可编程的架构来实现。这为嵌入式系统设计师带来了颇多的灵活性,并使他们能在其设计中以低成本的方案实现高整合度。

FPGA供应商也意识到了正转向串列埠的这一趋势,并正致力于为更多的开发商提供可用的高速串列技术。绝大多数的高阶FPGA产品中目前都有数Gb的串列I/O功能,该功能也正开始进入低成本的FPGA元件中。FPGA固有的可重新编程能力还为实现测试功能的测试工具提供一个真正的机会。开发和测试工具正涌现出来,这为设计师提供了掌握串列介面的行为和品质的新方法。这些新工具採用与高速串列技术指标(如BER测量)相关的测试类型,这就使得它们对以前由于知识面和採购相关仪器成本所限而没有考虑过的各类设计师来说都是有用的。

测试FPGA中的高速串列I/O

这些工具可用来时FPGA开发商测量串列I/O。图2为此类工具架构图。

图2:用于高速串列链路测试的嵌入式测试解决方案架构图。

该工具有叁个基本的部份组成:

1. 实现晶片上测试模式产生、BER测量和存取发射和接收器控制记忆体的测试核心;2. 测量软体;3. 简单的硬体介面,本例中用JTAG编程电缆来实现。

人们可以看到,利用该架构,透过适当地配置这叁个部份,就可以设立起一个测量例程来探测用Xilinx FPGA实现的高速串列链路工作情况。

这样的测试工具提供了进行叁个基本链路测量的能力,所有的都基于BER,其已被广泛地接受作为高速串列埠的最终测量。最简单的就是该工具可以提供链路BER测量。该测量在内部实现,并反映从FPGA内部的接收器所视的实际条件,而无须採用传统测量中通常使用的接触式探头来测量元件的接脚。

另一个感兴趣的测量是视图测试(图3详见本刊网站),这为迅速掌握链路裕度提供了一个简单的方式。透过在数据眼的单位间隔上重复进行BER测量,可以为用户提供BER与数据眼位置关係的图形显示。最终,透过将视图测量功能与发射和接收控制暂存器存取相结合,就能有效地对链路进行调整,来获得最佳的BER。

图3:能够测量链路裕度的视图测试。

嵌入式测试的内涵

嵌入式系统中对串列I/O的採用将对如何成立设计团队和採用什么工具产生影响。我坚信针对这一技术的嵌入式测试的特殊应用将为开发商带来有价值的帮助。在高速串列领域及以外的其它领域许多其它的可能性都与这一概念相关。很显然,随着半导体技术在复杂度和功能以及速度等方面的不断发展,嵌入式测试方案将为系统设计师探究系统提供真正的机会,不论是硬体还是软体。

实现嵌入式测试要求一定的灵活度,以便将全新的测试拓朴架构和新的测试方案整合在一起来实现跨度覆盖到半导体製造商和测试测量供应商的测试解决方案。儘管这些合作意味着将对产业带来挑战,但却能为位于竞争的价值点上的设计师带来全新的、具有价值的测量功能,这都将是不可否认的经济驱动力。

高速串行IO效率嵌入式测 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)