基于FPGA的LZO实时无损压缩的硬件设计

时间:04-30

来源:RF技术社区

点击:

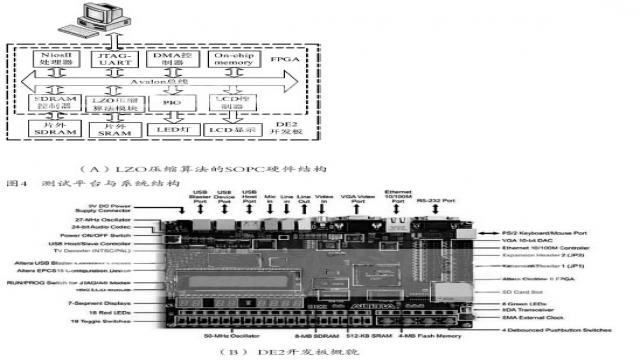

系统结构

3.2 开发板简介

测试与验证平台如图4(B)所示的DE2开发板,该开发板上的核心芯片为Altera公司的Cyclone II EP2C35 FPGA。选择该开发板作为测试平台主要基于以下考虑:拥有足够的片外存储资源(SDRAM 8MB、SRAM 512KB);拥有较丰富的片上逻辑资源(35K LEs);拥有丰富的可用于调试的外设(LCD、7-segment-displays);支持 Nios II嵌入式软核;成本较低。

3.3 测试结果及对比

针对LZO压缩算法模块和集成后的系统进行板级测试,一方面验证算法模块及集成后的系统的功能正确性,另一方面测试分析算法模块及集成后系统的性能。测试内容包括:数据压缩率(压缩后的文件大小/压缩前的文件大小),数据压缩速率(单个周期内处理的字节数)。

通过图5(A)可知,压缩率提升最大的是1.pdf文件,提升最小的是7.mp3文件(音频文件已经采用音频压缩算法压缩过了),除去最大值和最小值后取平均值,则压缩率提升为1.37%;通过图5(B)不难发现,压缩速率提升最快的为2.txt文件,提升最慢的为10.dll文件,除去最大值和最小值后取平均值,则压缩速率提升为4.81倍。

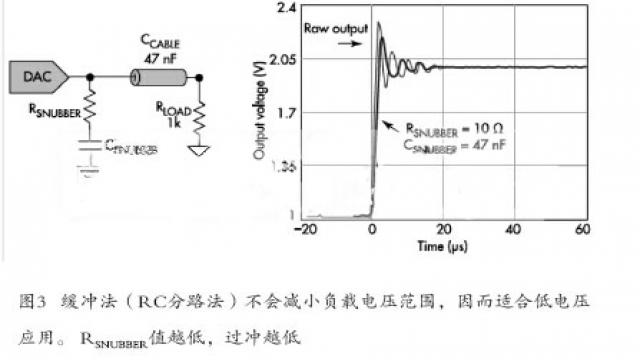

缓冲法结果分析

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)