利用高速数字分析仪和专用内存软件调试更高速率 DDR 信号

一、传统分析软件针对 DDR 信号的读写分离原理

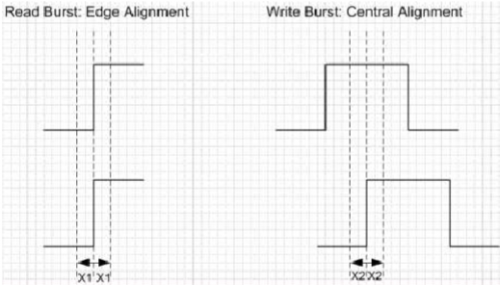

常用的 DDR 内存分析软件一般是通过 DDR 内存的 DQ 数据信号与 DQS 选通信号边沿 之间的时序关系来判别读与写的,即读突发时 DQ 信号和 DQS 信号边沿对齐,写突发时 DQ 信号和 DQS 信号中间对齐,如下图 1 所示,只要 DQ 信号和 DQS 信号之间的时序在[-X1, X1]范围内即认为是读突发,如果在[0.25*UI-X2,0.25*UI+X2]范围内,即为写突发,示波 器软件会进行优化设定 X1 和 X2 的值以尽可能准确的分离出读、写信号,不同示波器厂家 的软件也可能会有所区别。

图 1 常用的 DDR 内存分析软件所使用的读写分离方法

该方法对于速率较低的 DDR 内存信号来说会工作得很好,因为信号速率低,数据位间 隔 UI 就会比较大,也即读突发时的 DQ 和 DQS 的相对边沿位置数值与写突发时 DQ 和 DQS 的相对边沿位置数值相差比较大(相差 1/4 个 DQS 选通信号周期)。而当 DDR 信号速率越 来越高后,UI 将越来越小,此时即使是读突发周期,DQ 与 DQS 信号的边沿产生的偏移也 极有可能会被误识别为写突发,反之,写突发一样也可能会被错误的判别为读突发。

此外,由于电路板上的电子元器件的密集程度越来越高,而且内存类的芯片又都是 BGA 封装的,所以很多情况下难以在信号走线的最末端进行测试,从而导致测量到的信号出现反 射的现象,如下图 2 所示为一个 DDR3 信号的测试图示,左上和左下分别为写突发的 DQ 信号和 DQS 信号的眼图,右上和右下分别为读突发的 DQ 信号和 DQS 信号的眼图。从图中 可看出,写突发时 DQ 和 DQS 信号的眼图中也夹杂了读突发时 DQ 和 DQS 信号的眼图,原因正是读突发时 DQ 和 DQS 信号在接近电平 50%的位置有明显的台阶,此时 DQ 和 DQS 之间的时延将难以被准确测量和确定,也就是说使用传统的通过“读边沿对齐和写中间对齐” 的方法将难以精确的分离该情况时的 DQ 和 DQS 的读写信号。

图 2 某 DDR3 信号的读写信号眼图

二、基于高速数字分析仪及专用 DDR调试分析软件的内存测试方案

1、使用高速数字分析仪基于命令总线进行读写分离

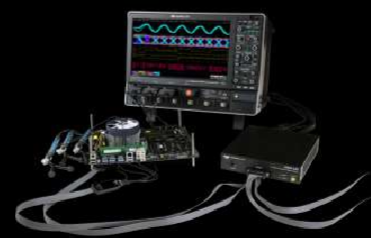

内存 DDR 接口都拥有并行控制总线信号,这些控制总线信号可以清楚的指明 DQ 和 DQS 信号是处于读突发状态还是写突发状态,以及这些信号来自于哪个芯片。所以可以通 过同时测试这些控制信号来对 DQ 和 DQS 信号进行读写分离。但一个明显的困难是,除了要测试 DQ 和 DQS 信号外,还需要额外再测试 4 个控制信号,若都使用模拟通道进行测试,则示波器的通道将不够用,而测试控制信号的目的是为了协助分离读写,所以完全可以使用数字探头来测试这些控制信号,然而新一代更高速率的 DDR,如 DDR4,速率比较高,达到了 3.2Gbps,传统的低速 MSO 将难以满足要求。为了应对这样的需求和挑战,力科推出了采样率高达 12.5GS/s 的高速数字分析仪及高带宽易于连接的数字探头。下图 3 所示为力科的高速数字分析仪 HDA125 与力科的 SDA820Zi-B 串行数据分析仪进行 DDR 信号测试验证的连接示意图。

图 3 力科的高速数字分析仪 HDA125

HDA125 具有 12.5GS/s 的采样率,存储深度大小取决于所连接的示波器,最多可配置16 条数字链路,探头的数字引线具有 3GHz 带宽,可采集 6Gbps 的信号,集成 9 英寸柔性“飞线”来连接难以抵达的连接点,且具有非常优异的负载特性(110k 输入阻抗和 0.12pF 的输入电容)非常适合于测试高速 DDR 内存信号。

2、DDR 内存专用调试工具包DDR

内存专用调试工具包是除了一致性测试工具包之外力科开发的另外一款专用于DDR 内存调试的工具,该工具更加注重于调试和分析,不是完全包括 JEDEC 规范要求的所有测试项目或者说只是 JEDEC 测试规范要求测试项目的一个子集。DDR 内存专用调试工具包具有如下功能和特点:只需按一个按钮即可实现 DQ 和 DQS 信号的读写分离(基于力科的 Qualify 一致性软件的读写分离原理);对 DQ 和 DQS 信号进行眼图和模板测量;对 D

高速数字分析仪内存软件DDR信 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)