基于示波器多重触发功能的串行丈量

大多数示波器提供了辅助触发系统或“B”触发器,答应用户定义范围更宽的条件。B触发器等待主(褹)触发发生,然后在越过自己的边沿门限时触发采集。这两者可以结合使用,以设置某些相当复杂的触发条件。例如,A可能在设备时钟输进线路上检测到一个毛刺,假如在输出上碰到上升沿或下降沿,可以触发B。假如没有这种转换,那么毛刺可以忽略。这两套条件结合使用,可以确定毛刺是否会引起不想要的状态变化。

直到最近,B触发功能一直限于边沿检测。但是对于复杂的新信号格式,特别是PCI Express和串行ATA等串行协议中使用的信号格式,需要触发系统的功能与其待处理的信号之间更好地匹配。

这些快速新协议中的错误可能来自多个事件的综合结果,如逻辑状态、偏移、瞬变、上升时间题目等。有时,必须规定非常精确的条件范围,以确定难以捕捉的错误。这要求触发工具系列能够分析更多的条件。可以采用双触发排列来解决这一题目,其中B触发系统与A系统基本上相同。只是在很多情况下,A条件相对简单,而在理想情况下,B触发器应能够评估比较复杂的一套指标,如只在其它逻辑信号处于规定状态时才会有效的事件数目等。但是,相关触发B一直缺乏A触发系统的灵活性。因此大多数示波器仅提供了非常简单的B触发器。

让两个触发器共同运行

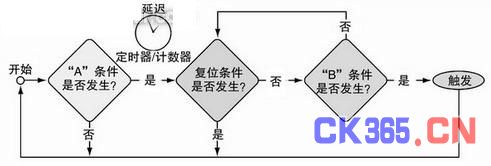

图1是简化形式的全功能双触发系统。

图1 全功能双触发结构

其中位于最后的触发器将帮助示波器捕捉有题目的信号,可能发生的条件如下:

是否发生A事件。用户可以规定边沿、削幅脉冲或很多其它条件;

在A事件发生时正确的逻辑状态(从最多两个不同输进中收集)是否生效;

是否满足A触发器和B触发器之间的延迟条件。“延迟”可以用时间或事件数目表示;

是否发生B事件。这可以是建立时间/保持时间超限、削幅脉冲或A触发器使用的同一类型列表中的任意选择;

在B事件发生时正确的逻辑状态(也从最多两个不同输进中收集)是否生效;

在整个过程中任何点上是否发生复位条件。复位将会绕过所有后续步骤,返回开头。

通过以上条件的依次执行明显进步了触发系统的灵活性。在同时考虑这两种事件条件及逻辑判定符时,可能的组合数可以达到几千种。这样,用户获得了一系列编程选择,从简单的单个输进上的边沿门限,到使用两个触发器、逻辑判定及时间或事件数目的复杂公式。

源自电脑编程领域的IF-THEN-ELSE构成了这类触发结构的概念模型。如图1所示,这些语句还包括其它判定符(如A和B之间的定时器/计数器)。不管B事件是否发生,在A事件之后随时都可以发生复位。

使用两个触发器找到一个脉冲

本文通过最新磁盘驱动器设计项目来介绍全面对称的双触发系统。

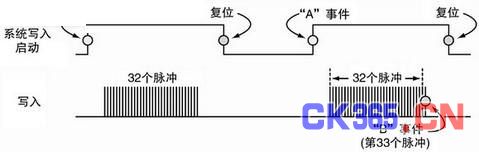

本系统中,读/写电路中的一个单元设计成在每个有效系统写进启动(WE)周期中执行一串32条写进命令。图2描述了较大的周期时间与导致数据写进的各个脉冲的关系。

图2 两个触发器捕捉偏离的写进脉冲

在这一新兴设计中,由于某些周期中发生了额外的脉冲,导致间歇性错误。尽管没有任何方式猜测什么时候会发生第33个脉冲,但通过某种手段捕捉不同的33个脉冲的顺序可以更简便地识别可能相关的其它系统事件。

一种解决方案是使用传统边沿触发器采集多次重复的WE周期及相关的写进脉冲顺序,检测每个WE周期的前沿,然后手动转动通过数据,找到有题目的周期。这种方法耗时长,而且不能保证在示波器波形的存储容量范围内错误脉冲只出现一次。工程师更希看的解决方案是只在发生33个脉冲周期时触发采集。其好处在于,感爱好的周期将自动显示在屏幕上,而不需麻烦的手动搜索。当然还会存储触发事件前和触发事件后的相关数据,但是触发发生的简单事实证实了存在33个脉冲周期。

这也正是双触发系统必不可少的地方。在这种情况下,磁盘驱动器设计职员需要设置一个相关触发器,其中WE信号的前沿(正向沿)作为A触发事件,而后沿则作为复位条件。

在这一过程中,A事件启动延迟计数器,计算脉冲数目。一旦产生了32个脉冲,它会使B触发器监测第33个脉冲。当检测到特定脉宽时,B系统便设成触发采集,这时,示波器触发并记录数据。假如没有第33个脉冲,复位条件会重新预备A触发器,再次启动整个流程。

假如B触发器只限于边沿检测,那么这种方法是不可能实现的。在这一过程中,不应忽视复位功能值,由于它决定着假如未能发生相应的A事件和B事件组合,示波器及其用户不会一直等下往。

变态的第33个脉冲是电路

示波器多重触发功能串行丈 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)