全面认识逻辑分析仪(上)

逻辑分析仪是一种多功能工具,可以帮助工程师进行数字硬件调试、设计检验和嵌入式软件调试。然而,许多工程师本应在使用逻辑分析仪时却使用了数字未波器,通常原因是他们更熟悉示波器。但是,逻辑分析仪在过去几年中已经取得了长足进展,对许多应用来说,它们可以比其它仪器在更短的时间内找到造成麻烦的根本原因。

数字示波器与逻辑分析仪比较

示波器和逻辑分析仪有许多类似之处,当然它们也有许多重大差异。为了更好地了解这两台仪器可以怎样满足您的特定需求,我们首先要比较一下各自的功能。

数字示波器是基本的通用信号观察工具。其高采样率和高带宽,使其能够在某个时间跨度内捕获许多数据点,测量信号跳变(边沿)、瞬态事件及小的时间增量。当然,示波器也能像逻辑分析仪一样查看相同的数字信号,但其一般用于模拟测量,如上升时间和下降时间、峰值幅度及边沿之间经过的时间。

示波器一般有最多4条输入通道。但在您需要同时测量5个数字信号时,或者处理同时拥有一条32位数据总线和一条64位地址总线的数字系统时,该怎么办呢?这时,您需要工具拥有多得多的输入。逻辑分析仪一般有34-136条通道。每条通道输入一个数字信号。某些复杂的系统设计要求数千条输入通道。业内也为这些任务提供了相应标度的逻辑分析仪。

与示波器不同,逻辑分析仪不测量模拟细节,而是检测逻辑门限电平。逻辑分析仪只查找两个逻辑电平。在输入高于门限电压(Vth)时,我们把电平称为“高”或“1”。相反,我们把低于Vth的电平称为“低”或“0”。在逻辑分析仪对输入采样时,它存储一个“1”或一个“0”,具体视相对于电压门限的信号电平而定。

逻辑分析仪的波形定时显示与产品技术资料中找到的或仿真器生成的定时图类似。所有信号都时间相关,因此可以观察建立时间和保持时间、脉宽、外来数据或漏掉数据。除高通道数外,逻辑分析仪提供了多种重要功能,支持数字设计检验和调试。

• 完善的触发功能,可以指定逻辑分析仪采集数据的条件。

• 高密度探头和适配器,简化与被测系统(SUT)的连接。

• 分析功能,把捕获的数据转换成处理器指令,并把它与源代码相关。

使用逻辑分析仪的方式与使用其它仪器相似,涉及的主要步骤有4个:连接、设置、采集、分析。

连接SUT

逻辑分析仪采集探头连接到SUT上。在探头的内部比较器上,输入电压与Vth进行对比,做出与信号逻辑状态(1或0)有关的判断。用户设置门限值,从晶体管与晶体管逻辑(TTL)电平到CMOS、发射器耦合逻辑(ECL)及用户自定义门限。逻辑分析仪探头分成多种物理形式。

带有“飞线束”的通用探头处理逐点调试。在电路板上要求专用连接器的高密度多通道探头可以采集高质量信号,而对SUT的影响达到最小。此外,对要求更高信号密度或无连接器探头连接机制的应用,我们推荐使用无连接器探头的高密度压缩探头,以便快速可靠地连接SUT。

逻辑分析仪的探头阻抗(电容、电阻和电感)成为被测电路上整体负载的一部分。所有探头都表现出负载特点。逻辑分析仪探头应给SUT引入的负载最小,同时为逻辑分析仪提供准确的信号。

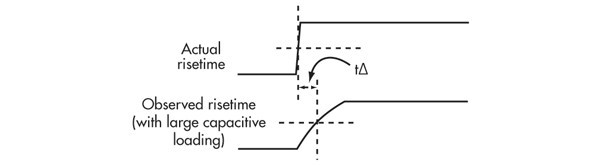

探头电容一般会“滚降”信号跳变边沿。这种滚降会降慢边沿跳变,下降量是图1中用“t?”表示的时间量。为什么这一点非常重要呢?较慢的边沿越过逻辑门限的时间比较迟,在SUT中会引入定时误差。在时钟速率提高时,这个问题会变得更加严重。

1.逻辑分析仪的探头阻抗会影响信号上升时间,可以测量定时关系。

[图示内容:]

Actual risetime: 实际上升时间

Observed risetime (with large capacitive loading): 观察到的上升时间(有大的电容负载)

在高速系统中,探头电容过高可能会阻碍SUT工作。应选择总电容最低的探头,这一点总是至关重要。还要指出的是,探头夹和线束会提高其连接到的电路上的电容负载。应尽可能使用正确补偿的适配器。

设置逻辑分析仪

逻辑分析仪是为从多引脚器件和总线中捕获数据而设计的。“捕获速率”一词指输入被采样的频次。其功能与示波器中的时基相同。注意在描述逻辑分析仪操作时,“采样”、“采集”、“捕获”这三个词经常互换使用。另外,数据采集或时钟模式分成两类。

第一类是定时采集,用来捕获信号定时信息。在这种模式下,逻辑分析仪内部的时钟用来对数据采样。数据采样速度越快,测量

数字信号模拟测量逻辑分析 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)