基于SOPC系统的虚拟示波器设计

序,对于最底层与硬件相关的操作,NiosⅡ提供了IOWR(base,offerset,data)和IORD(base,offerset)2个宏,分别用于对寄存器的读、写操作。这里,base为虚拟示波器驱动程序的基地址,其自动生成;offerset为指被操作的寄存器在该设备中的偏移地址。

2.3 嵌入式USB协议栈开发

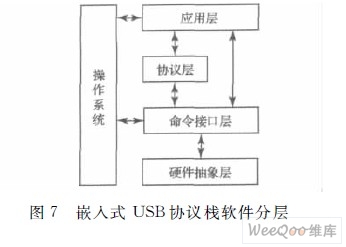

USB协议复杂,虚拟示波器系统开发的USB协议栈基于microc/os-Ⅱ,并采用了如图7的分层结构,以减少开发调试的难度。

硬件抽象层和命令接口层都与硬件相关,硬件抽象层负责对SX2的寄存器进行读写操作,而命令接口则实现与SX2的工作方式有关的操作;协议层与平台无关,其主要完成USB的枚举及各端口数据处理;应用层完成对提供调用的函数进行封装,应用层提供了简单的API接口,其利用senddata函数发送数据到主机,同时利用recdata函数从主机接收数据以及厂商请求的函数,上层程序只要简单地调试这3个函数而无需关注USB协议,即可完成虚拟示波器的USB通信。

3 虚拟示波器上位机软件设计

3.1 虚拟示波器USB通信的封装

虚拟示波器上位机程序采用LabWindows/CVI开发,其本身并不支持USB通信,因此采用了调用外部模块的方法。采用VC++编写程序,将USB通信底层函数进行封装,编译成DLL,再供LabWindows/CVI进行调用。为此,将动态链接库的头文件和DLL文件导入进工程,生成1个FP的驱动器,这时虚拟示波器系统就可以直接调用DLL里面提供的函数。

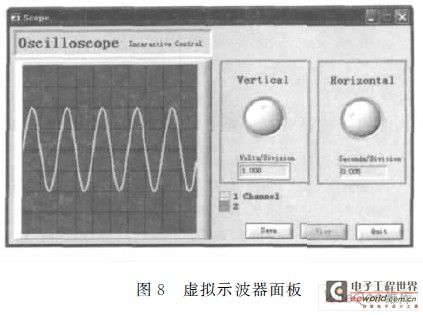

3.3 虚拟示波器面板程序的开发

图8中,用户对虚拟示波器面板上的垂直幅度调节、水平宽度调节等按钮操作时,系统会将相应的操作命令传送给下位机,并由下位机调节垂直幅度和水平时基等,从而实现用户对虚拟示波器系统的操作。

4 测试结果

采用FPGA处理器和ALTERA公司的NiosⅡ软核完成虚拟示波器系统设计后,进行了多次测试,其性能指标如表1所示。

由表1可知,该虚拟示波器达到了一般模拟示波器的指标。然而由于本系统采用虚拟仪器技术,在功能上增加单次采样、波形保存等功能,因此与普通示波器相比,其成本低廉,操作界面更友好、简便。

5 结论

本文以LabWindows/CVI为开发平台,设计了1种双通道虚拟示波器,该示波器利用FPGA 中嵌入的NiosⅡ软核构成的SOPC系统,完成虚拟示波器各模块的管理;利用嵌入式USB协议,配合片外的模拟信号处理模块,通过USB总线,完成各种波形数据的采集,经上位机软件完成了波形显示和数据分析,并实现了仪器的各种操作功能。实际测试结果表明,该虚拟示波器达到了或优于一般模拟示波器的性能指标。

参考文献:

[1].C1 datasheethttp://www.dzsc.com/datasheet/C1+_2455447.html.

[2].LTC2289datasheethttp://www.dzsc.com/datasheet/LTC2289_1104294.html.

[3].CY7C68001datasheethttp://www.dzsc.com/datasheet/CY7C68001_1097509.html.

[4].RISCdatasheethttp://www.dzsc.com/datasheet/RISC_1189725.html.

SOPC系统虚拟示波 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)