基于正交矢量放大的MRS信号采集模块设计---- 采集模块硬件设计(二)

4.3锁相环电路

4.3.1倍频电路设计思路

CPLD的FLASH中存储的正弦波的一个周期用256个点来输出,而正弦波的频率要求是在1300Hz~3000Hz范围内可调,步长为0.1Hz.这就要求FLASH模块的时钟频率在333KHz~768KHz范围内按步长25.6Hz可调。CPLD用的外部晶振为125MHz,如果这个时钟频率由CPLD分频产生,不能达到设计要求。但是CPLD可以实现频率在1300Hz~3000Hz范围内按步长0.1Hz可调,再把这个频率进行256倍频就可以达到设计要求了。

4.3.2锁相环电路芯片选择

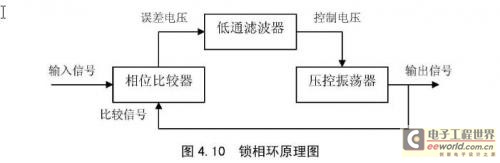

利用锁相环可以实现非常稳定的倍频电路。锁相环是一个相位负反馈的闭合环路,其频率跟踪原理图如图4.10所示.

锁相环是由相位比较器(也称鉴相器)、低通滤波器LPF和压控振荡器VCO三个环路部件组成的一个反馈控制系统。相位比较器(也称鉴相器)对基准输入信号和压控振荡器引入的信号进行比较,当基准信号和压控振荡器信号频率与相位相同时,鉴相器的输出为零;当两信号的频率和相位不同时,鉴相器的输出就产生一个误差电压,这个误差电压经过滤波环节,控制压控振荡器,使其输出频率和相位与输入信号的频率和相位绝对匹配,锁相环路既实现了“锁相”。

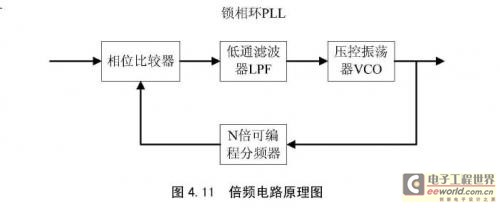

将压控振荡器输出信号经过N分频后再输入到相位比较器中,那么锁相环锁定后压控振荡器输出的信号频率就是基准信号频率的N倍,这就是锁相环实现倍频电路的原理,如图4.11所示。

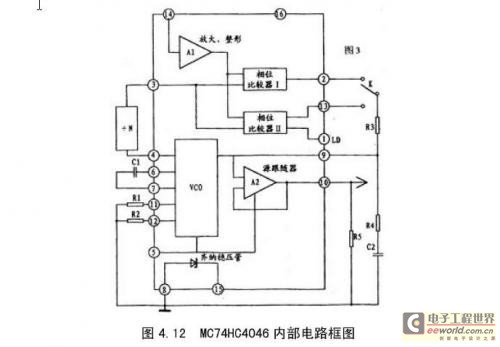

现在常使用集成电路锁相环74HC4046,它的内部电路框图如图4.12所示。

主要由相位比较器Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。比较器Ⅰ采用异或门结构,当两个输人端信号Ui、Uo的电平状态相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;反之,Ui、Uo电平状态相同时(即两个均为高,或均为低电平),UΨ输出为低电平。当Ui、Uo的相位差Δφ在0°-180°范围内变化时,UΨ的脉冲宽度m亦随之改变,即占空比亦在改变。从比较器Ⅰ的输入和输出信号的波形(如图4.13所示)可知,其输出信号的频率等于输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°相移。对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使锁定范围为最大。本设计中要产生的时钟频率为占空比为50%的方波,所以使用相位比较器Ⅰ.

74HC4046锁相环采用的是RC型压控振荡器,必须外接电容C1和电阻R1作为充放电元件。当PLL对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2.由于VCO是一个电流控制振荡器,对定时电容C1的充电电流与从9脚输入的控制电压成正比,使VCO的振荡频率亦正比于该控制电压。当VCO控制电压为0时,其输出频率最低;当输入控制电压等于电源电压VDD时,输出频率则线性地增大到最高输出频率。VCO振荡频率的范围由R1、R2和C1决定。由于它的充电和放电都由同一个电容C1完成,故它的输出波形是对称方波。

4.3.3 74HC4046电路实现

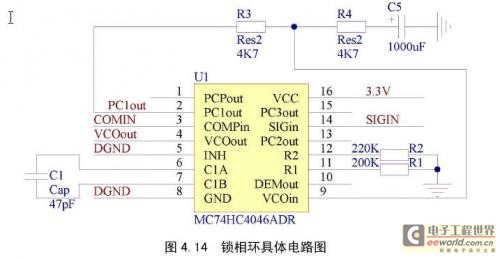

锁相环实际电路连接图如图4.14所示。CPLD分频产生1300Hz~3000Hz范围内同Lamor频率相等的信号,输入74HC4046的14脚输入端。4脚VCO输出频率经过CPLD中的256倍分频器,再输入4脚相位比较器输入端。相位比较器的输出2脚经过RC低通滤波器输入VCO输入端,组成锁相环路。

74HC4046的VCO频率范围由外接电阻、电容决定,公式如下:

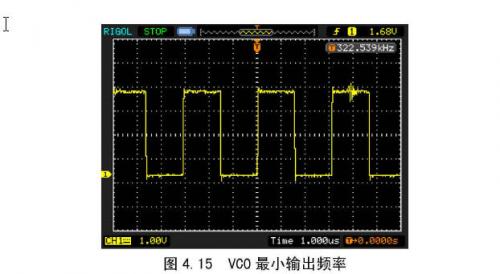

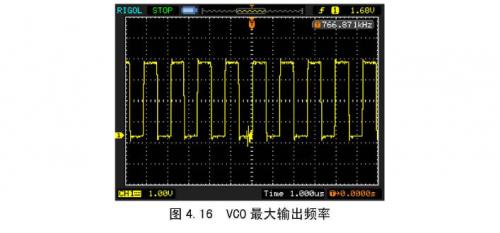

根据74HC4046数据手册,确定外围电容、电阻参数为:C1 = 47pF,R1 = 200kΩ,R2 = 220kΩ。最终测得VCO输入电压为0和VDD时,VCO输出波形如图4.15和图4.16所示。

4.4低通滤波器电路

4.4.1 LPF电路设计

要求锁定放大器改善信噪比的作用主要由低通滤波器来实现。低通滤波器的通带宽度越窄,抑制噪声的能力越强。即使LPF的截止频率很低,其频率特性仍然能够保持相当稳定,这是利用LPF实现窄带化的优点。为了适应不同的被测信号频率特性的需要,LPF的截止频率常做成可调的。

传统的滤波器一般采用分立器件来实现,电阻、电容的选取和匹配以及优化灵敏度等问题非常复杂,而且器件参数容易随时间和温度的变化而产生漂移。MAX260系列可编程开关电容滤波器,在一个芯片上集成了运算放大器、电阻和电容,设计时已经优化了灵敏度而且匹配好了元件,因而极大的简化了滤波器的设计,把需要的控制参数加载到芯片以后,几乎不需要外接元件,就可以方便的实现各种滤波器功能.

4.4.2 LPF电路芯片选择

综合考虑,选择MAX260实现低通滤波器。

MAX260系列芯片主要由放大器、积分器、电容切换网络(SCN)和工作模式选择器组成,积分器、电容切换网络和工作模式选择器分别由编程数据M0,M1、F0~F5和Q0~Q6控制。每个芯片内部都含有两个独立的可编程二阶开关电容滤波器,它们可以单独使用,也可以级联成一个四阶的滤波器,滤波器A和B可以采用内部时钟,也可以采用外部时钟,每个滤波器的独立时钟输人端可以连接晶振、RC网络或外部时钟产生器,芯片对外部时钟的占空比没有要求。可编程的参数有中心频率、品质因数和工作模式,输人时钟频率与6位编程代码F0~F5一起决定滤波器的中心频率或截止频率,其中,时钟频率和中心频率之比可实现64级程控调节,品质因数可实现128级程控调节,中心频率和品质因数以及工作模式都可独立编程,互不影响,片内开关和电容提供反馈以控制每个滤波器的中心频率和品质因数,内部电容的开关速率是影响这些参数精度的主要因素。MAX260可以实现中心频率或截止频率在0.01Hz~7.5kHz范围内可调,能够达到设计的要求。

正交矢量放大MRS信号采集模块锁相环电路低通滤波电 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)