雷达系统的数字基带和射频域集成挑战

可重新配置的雷达系统采用FPGA和DSP制式的数字技术。数字技术与射频技术结合可以实现极高的灵活度,适应当前雷达应用对不同波形和配置的严苛需求。因此,基带工程师团队一直应用与射频团队不同的设计方法和测试工具。不同技术的结合为系统集成测试带来了重大挑战。

本文将介绍一个应用单一测量平台应对上述挑战的方法。该平台能够帮助雷达系统集成商方便地验证和调试其设计。该方法支持在雷达发射机或接收机路径中进行矢量信号分析仪(VSA)测量,以及结合逻辑分析仪测量FPGA硬件、结合示波器测量模拟中频或射频电平、结合信号(频谱)分析仪测量射频激励器和接收机链路。三种仪器都可以导出捕获的信号并输入通用分析环境,以帮助设计人员查明混合信号链路任意点可能存在的问题,最终成功完成系统集成。

线性调频雷达设计实例

脉冲压缩是扩展雷达系统探测距离并提高分辨率的一个常用方法。对脉冲进行频率或相位调制,脉冲每个部分都将具有各自独特的频率或相位编码。借助独特的频率和相位分量,我们可以更轻松且更彻底地分离目标回波,排除回波信号频域重叠的干扰。脉冲压缩可以降低脉冲的峰值功率要求,并减少雷达脉冲被探测到的概率。在整个脉宽内以“线性”方式对脉冲进行频率调制是一种脉冲压缩类型。“线性”频率调制也称为“线性调频雷达”频率调制。

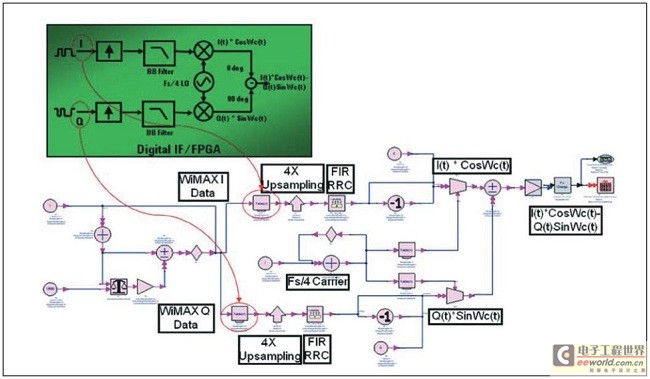

使用安捷伦的SystemVue可以获得高水平的雷达基带设计(参见图1)。生成I和Q矢量调制线性调频雷达信号,进行四倍因数上采样,应用根升余弦滤波并上变频至数字中频。使用SystemVue生成硬件描述语言(HDL)代码,推动Xilinx Virtex-4 FPGA基带设计的FPGA实现。

图1:具有数字基带功能的线性调频雷达发射机部分。

然后,导出数字中频信号并输入数模转换器。最后,生成的模拟中频信号上变频至射频频率,经过功率放大器并由天线发射。

高级设计仿真

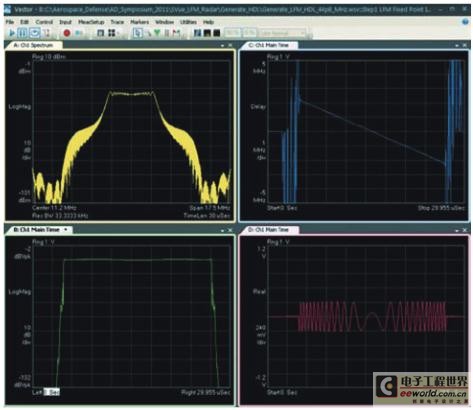

FPGA实现前可进行高级设计仿真。将仿真数字中频信号输入89600矢量信号分析(VSA)工具(结果如图2所示)。在本例中,左上角面板显示的是需要的频率频谱内容,右上角面板显示的是整个雷达脉宽内的线性频移,左下角面板显示的是雷达脉冲幅度时域视图,右下角面板显示的是传统的数字矢量调制实部视图。四个视图是比较真实硬件测得信号的“黄金标准”。

图2:在VSA应用软件中解调仿真数字中频信号。

查看整个信号路径

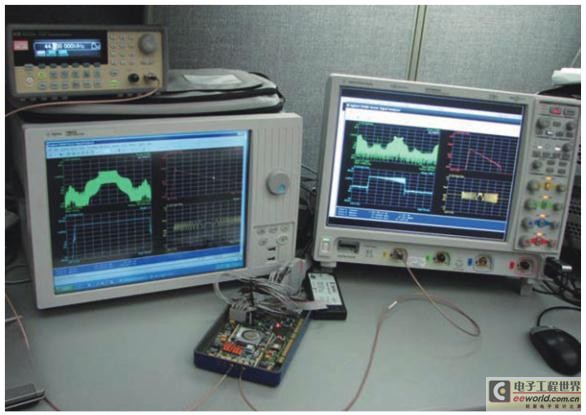

基带设计采用FPGA方式实现,因此在矢量调制路径中输入不同信号并结合逻辑分析仪可以深入测试FPGA。测试设置如图3所示。左侧为逻辑分析仪,通过“飞线”将探头连接至Digitech ExtremeDSP Xilinx Virtex-4平台的0.1英寸头引脚。飞线探头可以为每个数字数据信号提供独立的同轴连接。多个接地连接可以确保探测到的信号具有良好的完整性。

图3:逻辑分析仪探测内部FPGA信号(L),示波器探测数模转换器输出模拟中频(R)。两者都运行着VSA软件。

右侧为示波器,模拟中频信号通过SMB连接器由DigiTech平台的数模转换器输出,然后经由一条同轴电缆进入示波器。请注意,Xilinx USB JTAG编程电缆用于连接Virtex-4 FPGA所在位置的JTAG链路。最终,JTAG连接将用于切换FPGA内部的多路复用器,以通过内部FPGA路由资源获取所关注的信号。

在本例中,Xilinx应用ChipScope Pro “Core Inserter”通过内部FPGA多路复用器测量核心和FPGA内部路由资源定义探测点。首先,该工具支持用户定义测量核心类型、信号丛集的数量、用于调试信号的引脚数量以及输出调试信号的FPGAI/O引脚。

我们可以通过经过上变频和滤波的I和Q检测FPGA信号,也可以激励数模转换器的数字中频检测FPGA信号。然后,称为“FPGA动态探头”的逻辑分析仪工具与FPGA测量核心结合,可支持设计人员进行有意义的测量。

逻辑分析仪FPGA探测工具可以大幅简化测量过程。首先,该工具支持用户通过JTAG连接直接从逻辑分析仪接口向FPGA下载.bit格式的FPGA设计文件。

其次,该工具可以从Xilinx生成的.cdc文件导入内部探测到的FPGA总线和信号名称。.cdc文件由Xilinx ChipScope Pro Core Inserter应用软件创建。之后,称为“自动引脚映射”的流程将使用逻辑分析仪探测FPGA输出引脚的调试信号,并自动“映射”至逻辑分析仪的输入通道。设置逻辑分析仪以获得适合的已定义时钟输入,阀值电平应匹配FPGA输出电压电平,逻辑分析仪捕获模式应匹配FPGA调试信号输出。设计人员可以选择要查看的信号丛集。本例选的是数模转换器输入。

现在,逻辑分析仪捕获一条数字信号迹线,如图4左侧所示。逻辑分析仪使用了“图表”显示模式,其中总线的十六进

数字基带射频域逻辑分析仪矢量信号分析 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)