面阵CMOS图像传感器LUPA4000的驱动设计

随着CMOS集成电路工艺的不断发展和完善,CMOS图像传感器发展非常迅速。CMOS图像传感器具有低成本、简单的数字接口、运行简易、高速率可以实现智能处理功能等特点而得到广泛应用;又因其具有噪声低、功耗小、动态范围宽、光谱灵敏度高、超微型化、数字化以及易实现商品化等特点,特别是他将图像传感器阵列、时序控制电路、信号处理电路、A/D转换器以及接口电路等集成于一体,真正实现了单芯片成像,LUPA4000是一款典型的大面阵宇航级的CMOS图像传感器,本文主要描述在本设计中所做的两项主要的工作:在软件上利用VHDL语言描述图像传感器LUPA4000的驱动时序的思想以及在硬件上设计其外围电路的方法。

1 LUPA4000图像传感器

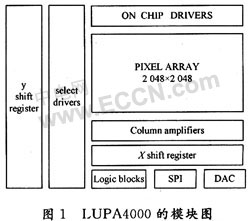

LUPA4000是Cypress公司生产的一款400万像素的CMOS面阵图像传感器,凭借着其在读出速度快(66 M/s)、功耗低(不高于200 mW)、空间应用的可靠性好(能够在强辐射环境中工作)等方面的优势,LUPA4000主要用于天文观测等领域中发挥着其绝对的优势;此外,他还广泛应用于机器视觉以及医疗影像中。在不开窗口的情况下速度可以达到15 f/s;片上集成了2块A/D转换器用来提高像素的读出速度是其又一显著特点;同时,LUPA4000又提供了开窗口模式用以提高读出的速度,所谓开窗口模式是指LUPA4000可以通过对SPI(SPI下文有介绍)可编程特性任意改变他的读出阵列大小。在特定情况下LUPA4000的另一个优越性体现在他可以进行双斜率积分实现对第一次积分的补偿;美中不足的是LUPA4000是一款单色的传感器芯片。这里用图1来说明他的工作原理:

从图1上可以看到,LUPA4000主要有以下几个部分组成:一个像素阵列单元、X方向寻址寄存器以及2个Y方向的寻址寄存器(图上画了1个)、SPI(Serial-Parallel-Interface)列信号放大器等。采用同步快门工作模式,其具体的工作流程主要分为3个步骤:

(1)在图像传感器工作之前,首先应上载SPI;SPI俗称内部寄存器,他决定了图像传感器的读出方向以及是否进行开窗口读出等;上载结束之后,会输出一个eos_spi信号意味着寄存器上载完成。

(2)上载结束之后,图像传感器就可以正常工作。当图像传感器接受到外界的光信号之后,光积分区域便由reset,mem_hl,precharge,sample四个信号控制,实现光电转换,然后把电信号储存到每个像素单元里;

(3)积分结束之后,就进行信号的处理与读出,这是工作最重要的部分,这些环节由sync_y,clock_y,no-rowsel,pre_co,sh_co,sync_x,clock_x控制。

sync_y信号高电平的到来意味着1帧图像开始读出;clock_y信号为高电平时则意味着1行像素开始读出。当1行像素读出时,会有1个行开头时间(ROT),由no-rowsel,pre_co,sh_co三个信号来控制,这个时间时为了确保输出数据的稳定性,原则上说,ROT越短越好;然后sync_x为高电平的时候,开始行读出,行读出由信号clock_x控制,clock_x时一个66 MHz的周期信号,每个周期读出2个像素;如此反复,当读完最后一行的时候,会输出一个eos_y信号,意味着1帧读出的结束。这就构成了一个循环。

2 时序的设计

根据上面的叙述,就可以清楚LUPA4000的基本工作原理。在具体的时序设计过程中,采用自顶向下(top-down)的设计方法,产生这些数字信号。所谓自顶向下的设计是从系统级开始,把系统划分为若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元,直到可以直接用基本元件实现为止。自顶向下的设计方法方便从系统级划分和管理整个项目,使得复杂数字电路的设计成为可能,并且可以减少设计人员,避免不必要的重复设计。

为了能让其正常工作,需用1块CPLD或者FPGA,通过VHDL语言产生出上述所需要的信号,然后将其送给LUPA4000。可以根据上述所分析的LUPA4000工作的3个阶段,通过有限状态机(state machine)产生具体的信号。状态机是由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心,属于一种时序逻辑电路。通常状态机由3部分组成:当前状态寄存器、下一状态组合逻辑、输出组合逻辑。LUPA4000的具体状态转换如图2所示。

由于LUPA4000所需要的资源不大,故本设计采用1块Altera公司的MAXⅡ系列EPM1270T144C5。本设计使用VHDL语言编写程序代码,利用Altera公司的配套软件QuartusⅡ进行仿真,其具体的仿真结果如图3所示。

其中clk为输入信号,由有源晶振提供;mem_hl,precharge,reset,sample为CPLD输出给LUPA4000的积分信号;sync_y,clock_y,norowsel,re_co,h_co,syn

图像传感器 相关文章:

- 拍摄爱好者的福利 CMOS图像传感器之HDR渲染解析(01-17)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)