一新型无损箝位电路在单端正激电源中的应用

摘要:介绍了一种新型无损箝位电路在单端正激电源中的应用, 详细分析了工作原理,并给出了实验结果。 叙词:无损箝位 Abstract:Application of a new lossless clamp circuit for single ended forward converter is introduced, the operation principle of this circuit is analysed in detail,and the experiment result is also given. Keyword:lossless clamp

1 引 言

在各种隔离式DC/DC变换器中,单端正激式变换器是其中最简单且适合大电流输出的一类,因而正激式变换成为低压大电流功率变换器的首选拓扑结构。但因其高频开关变压器磁通工作在磁滞回线的一侧,必须进行磁复位,以确保励磁磁通在每一个开关周期开始时处于初始值。同时由于工作在高频状态下,开关变压器漏感、分布电容等寄生参数的影响不能忽略,在开关转换瞬时,电抗元件的能量充放致使功率器件承受很大的热和电应力,并可导致开关管的电压过冲,这不仅意味着设计人员必须选用昂贵的高耐压功率开关管,同时也给电源的可靠性带来潜在威胁。为此常常还需设置各种缓冲吸收电路,但这降低了变换器的工作效率。

为了解决单端正激式开关电源中的磁复位与漏感储能问题,传统的解决方案有以下几种:

(1)、采用辅助绕组复位电路;

(2)、采用RCD箝位复位电路;

(3)、采用有源箝位复位电路。

其中方案1要求辅助绕组与初级绕组必须紧耦合,实际上因漏感的存在电路中仍需外加有损吸收网络,以释放其储能;方案2是一种有损复位箝位方式,因其损耗的大小正比于电路的开关频率,(和方案1中外加有损吸收网络一样)这不仅降低了电源本身的效率,也限制了电源设计频率的提高;方案3中需要附加一复位开关管与相关控制电路,增加了电路复杂性的同时,也带来了附加电路损耗与总成本的上升。

本文介绍一种新型无损箝位电路,无须额外附加辅助开关管,电路简单,可有效降低功率管的电压应力,箝位效果优异,且有利于电源工作效率的提高。

2 工作原理

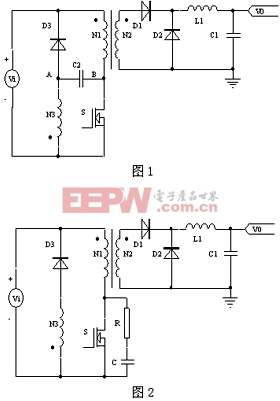

新型无损箝位电路(图1)与上述方案1(图2)中采用辅助绕组的传统方法相类似,不同之处是增加一个箝位电容C2,但功率主回路上无需外加有损吸收网络。传统的方法是在变压器中附加一个去磁绕组N3,它与二极管D3串联后接到电源输入正极,N3起到去磁复位作用,功率管S漏源间并联的RC网络,用于吸收变压器的初级漏感储能,防止产生过电压尖峰,保护功率管S免被击穿,见图2所示。图1中的箝位电路由辅助箝位绕组N3、箝位二极管D3、箝位电容C2组成。辅助箝位绕组N3的与初级绕组N1相同,目的是为了实现当功率开关管S漏源间电压VS上升到2VI时,加在初级绕组N1上的电压等于VI,因N1、N3匝数相等,箝位绕组N3的电压也必然是VI,此时D3恰好正偏导通。

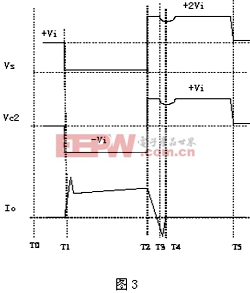

下面结合图1与图3具体分析新型无损箝位电路的工作原理。

1) T0时刻为初始状态,设功率开关管S处于关断状态,此时(B点电压)VS等于VI,箝位电容C2通过初级绕组N1、箝位绕组N3被充电至VI,电容极性为左负右正。

2)在T1~T2期间,功率管S导通,由于箝位绕组与初级绕组电压相同,参照图1所示的同名端可知,VA为-VI,二极管D3反向偏置截止。在此期间,变换器实现功率的变换,能量从初级传到次级。

3)在T2时刻,功率管S关断,变压器中的漏感与磁化储能给功率管等寄生分布电容充电,(B点电压)VS最终上升到2VI,A点电位也从- VI 上升为+VI ,若此时B点电位进一步上升,二极管D3将正向偏置导通,功率管S漏源间的电压VS通过电容C2和二极管D3得到有效箝位。

4)在T2~T3期间,反射在初级的负载电流Io下降,其下降的速率由初级与次级间的漏感决定,该电流通过箝位电容C2、箝位二极管D3回流至电源,流过电容C2的电流引起其端电压上升(设其增量为dVS),导致B点电位变化为2VI+dVS。

5)在T3时刻,由于出现输出二极管D1的反向恢复,反射到的初级电流Io出现负值,箝位二极管D3停止导通,因功率管S的漏源间存在输出电容Cp,(B点电位)VS出现下降直到输出二极管D1反向反射电流小于初级磁化电流并在T4时刻等于零为止。

6)在T4~T5期间,正在减少的正向磁化电流将引起B点电位VS再次向2VI上升,直到箝位二极管D3再导通,将VS箝位在比2VI稍高的电位上。

7)在T5时刻,初级磁化电流减为零,箝位电容C2通过初级绕组N1、箝位绕组N3向电源VI放电,回送电容储能,VS跌至VI。

8)下一时刻重复以上过程。

3 关键电路参数设计

(1)箝位电容计算

从上文分析可知,箝位电容C2的取值决定了功率管漏源间电压VS超出VI值的多少,超出的电压dVS近似计算方法见式 (1):

dVS =0.5(Io/Nps)(T2-T3)/C (1)

式中 Nps是初次级匝比,Io是负载电流。

电源 应用 端正 电路 无损 新型 电源,DC DC 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)

- 高效地驱动LED(04-23)

- 电源SOC:或许好用的“疯狂”创意(07-24)