基于0.5μm BCD工艺的欠压锁存电路设计

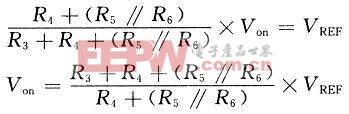

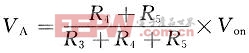

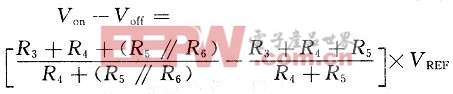

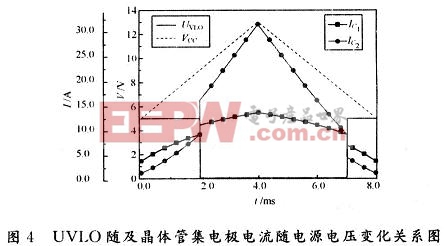

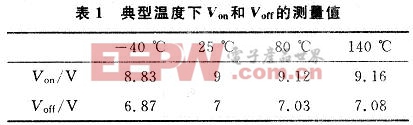

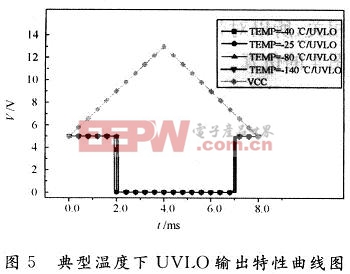

=R8,此时: 只要适当选择M7,M8管的宽长比和电阻R7,R8的大小,就能使得UVLO仍然输出高电平,从而达到关断基准电源和锁存整个芯片的目的。 (3)当VCC上升到大于Von时,由于Q2比Q1的跨导大,所以,IC2迅速超过IC。假设带隙基准比较器中各个镜像对管都处于饱和区,则同第二节(1)中的分析。同一直流通路上的电流ID6较ID4小,这是不可能的,所以这会驱使M4管进入线形区。这样,带隙基准比较器输出X点电位上升到高电平,经反相器反向后使得M9管关闭。A点电位进一步被拉升,从而确保UVLO输出为低电平,使得芯片正常工作。正是由于镜像对管对流过它们电流差异具有高度敏感性,所以这种UVLO电路反应速度很快。当VCC由高压慢慢变低时,同样也有三种情况: ①当VCCVoff时,同上一情况中的(3),IC1IC2,M4工作在线形区,M9工作在截止区,UVLO输出为低电平。 ②当VCC下降到接近Voff时,类似于前面提到的(2),这时IC1△IC2,带隙基准比较器中的各个镜像管都工作在饱和区,X点的电位同样可以驱动M7管导通,且使其首先进入在线性区(注意同前面提到的(2)的区别),M9管关闭,UVLO输出仍为低电压。 ③当VCC下降到Voff时,IC1>IC2,M6进入线性区,X点电位被拉低,经过反向器作用,M9管导通,此时进一步达到低压锁存的效果。应当注意的是此时的Von≠Voff。 从上面的分析可知,当晶体管Q1和Q2的集电极电流相等时,带隙基准比较器各个镜像对管都工作在饱和区,此时A的电压大小非常关键。设此时A点电压为VREF,Q1,Q2集电极电流为: 对于双极晶体管的基极发射极电压,有以下关系: 而IS∝SE,其中,是晶体管发射极面积。由于Q1的发射极面积是Q2的6倍,所以,式中: 由于VBE具有负的温度系数,而VT具有正的温度系数,只要适当选择电阻R1、R2的比值,就可以实现几乎零温度系数的带隙电压。现在再分别计算Von和Voff。 由上面分析可知,当电源电压VCC升高到尚未达到UVLO的开启电压Von时,UVLO输出高电平,且M9处于导通状态(忽略其导通电阻),此时A点电压为: 只有VA>VREF时,UVLO的电平才会翻转,这样就得到了开启电压的门限值Von, 一旦VCC>Von,M9管关闭,这时A点电压: 大于VREF,使得UVLO更稳定地输出低电平。同理,可以得出UVLO的关闭电压值Voff: 那么UVLO的滞回区间为: 3 电路仿真与分析 使用HSpice电路仿真软件在CSMC 0.5μm BCD工艺库下对UVLO电路进行仿真。由上面分析可知,UVLO电平翻转与晶体管Q1,Q2集电极电流变化速度快慢密切相关,所以对带隙基准晶体管上集电极电流变化做了如图4的仿真。从图4中可以明显看出,在2 ms以前,IC1>IC2,UVLO输出高电平。在2 ms时,两个晶体管的电流都急剧变大,但是由于Q2管的跨导比Q1管小,所以很快,IC1IC2,UVLO输出为低电平。下面可同理推出。 因为DC-DC芯片应用的温度范围比较大,而且工艺中的电阻、晶体管等受温度影响也比较大,所以在实际设计中,应当充分考虑到这点。在此对UVLO不同温度下进行仿真,尽可能把滞回区间的误差缩小到很小的范围内,以满足DC-DC芯片在宽温度范围内工作。表1和图5是对本文所设计的UVLO电路在-40℃,25℃,80℃和140℃下的仿真结果。从中可以看出,在25℃时,Von=9 V,Voff=7 V,滞回区间是2 V。在其他温度下的偏差最大也不超过0.2 V,可见其最突出的优势是可以在宽温度范围内工作而不失精度。 除此之外,当芯片发生欠压锁存时,芯片的功耗也是非常小的。这主要是因为当芯片发生欠压锁存时,芯片的其他部分都不工作,也就不消耗功率,UVLO电路的主要功耗是流过带隙晶体管和R3,R4,R5,R6电阻的电流所产生,只要适当地调节这些电阻阻值就可以把功耗降低到最低,但是考虑到版图的面积,实际仿真中的功耗可减小到150μW以下。 4 版图设计 使用CSMC 0.5 μm BCD工艺技术,对UVLO电路设计版图。由于利用带隙基准原理,在要求精度较高的情况下,设计时应注意UVLO模块与其他模块隔离。与传统的UVLO电路相比,最显著的提升就是版图面积大大缩小,只要工艺中包含高阻值的电阻类型,这种优势就更为突出。 5 结 语 在此针对DC-DC电源管理系统所必须的欠压所存功能,详细介绍一种新的改进UVLO电路,相对于传统的UVLO电路,它最突出的优点是不使用额外的带隙基准源和复杂的数字逻辑,因此节省了芯片面积。HSpice仿真结果表明,它在-40~+140℃范围内最大失真不超过2 %,因此可以在宽温度范围内工作。基本适用于各种类型的电源管理类芯片,对工艺要求也不高。

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)