低输入电压DC-DC升压转换器的启动电路

摘要:针对DC-DC升压转换器在低输入电压下无法正常工作的问题,提出了一种基于电容自举原理的低输入电压的启动电路。采用CSMC公司的0.5μm CMOS混合信号工艺库进行电路设计与仿真,考虑到结构复杂的振荡器在较低电源电压下不能理想工作,同时为减小电路功耗,电路采用两种不同简单结构的环形振荡器实现电容自举,并利用反馈控制模块进行合理的逻辑控制。仿真结果表明,O.8 V低输入电压时,通过升压电路转换,可将Vdd升高到2.4V;振荡信号变化时,输出电压变化微小,可以为DC-DC升压转换器提供稳定的电源电压。

关键词:低输入电压;DC-DC升压转换;启动电路

在遥控器、MP3播放器、手持式设备等电子产品中,通常使用单节AA电池或充电电池供电,电压仅约0.8 V,无法保证DC-DC器件正常稳定的工作。本文提出了一种基于电容自举原理的低输入电压启动电路,在0.8 V的低输入电压下工作,通过DC-DC升压转换,将Vdd升高到2.4 V,并采用从Vdd供电的方式,为后续的DC-DC升压电路的各个模块提供稳定的电源电压,以保证自举(Boost)器件满足设计要求。

1 启动电路结构设计

图1为启动电路结构框图。其中,电感L、电容C、续流二极管VD以及功率MOS管构成典型的DC-DC升压电路,虚线框内是启动电路各个功能模块。为减小电路功耗,该启动电路采用2种不同结构的振荡器,其中振荡器0SCl工作在低电源电压下,利用该振荡信号驱动自举电路,逐步升高至功率管的栅电平,从而实现功率管的导通与截止。应用boost电路的升压功能,使Vout逐渐增大。

启动电路各个模块的电源均由输出电压提供,即Vout是启动电路的电源电压。随着Vout的升高,振荡器0SC2启动,通过反馈控制模块与选通电路的共同作用,0SC2的振荡信号得以取代0SCl信号控制功率管,使Vout进一步增大。最终输出较稳定的电压,为DC-DC升压转换器提供初始工作电压。

采用无锡上华(CSMC)公司0.5μm CMOS混合信号工艺库进行电路设计与仿真。MOS管阈值电压分别为VTHN=0.7 V,VTHP=-0.95 V。

2 启动电路功能模块设计

2.1 振荡器

在较低电源电压下,结构复杂的振荡器不能理想工作。因此,2个振荡器均采用结构简单的环形振荡器。环形振荡器由3个或更多奇数个反相器首尾相接构成。设反相器传输延迟为tpd,反相器级数为N,上升时间为tr,下降时间为tf,则发生振荡的条件是:2Ntpd>>(tr+tf)。如果不能满足振荡条件,振荡器前后输出波形将相互叠加,最终衰减为零。振荡周期T=2Ntpd,反相器的传输延迟时间为:

式中,kp=μpCoxWp/Lp;kn=μnCoxWn/Ln;CL为反相器的负载电容,包括反相器本身的寄生电容,连线电容和负载电容。

环形振荡器结构简单,可以实现高频振荡。但是振荡频率不可控,随电源电压变化显著。这是因为,电源电压的升高直接影响着反相器充放电电流的大小。当电压升高,充放电电流增大,缩短了充放电时间,使振荡频率增大。通过在振荡器中加入RC延迟环节,方便调节振荡频率。

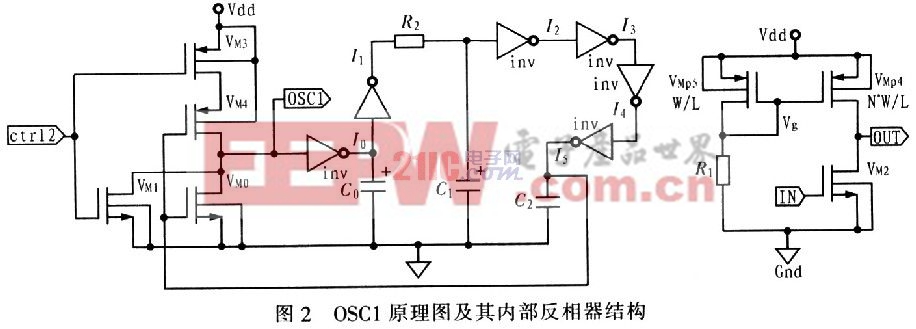

OSCl原理图及其内部反相器结构如图2所示。因为振荡器OSCl的频率随Vdd变化明显,如果只使用一个振荡器,最终频率将达到初始频率10倍以上,增大电路功耗,所以电路中采用2个振荡器。当Vdd上升到可以保证0SC2正常工作,频率输出稳定时,关断OSCl,改用OSMC2控制功率管。所以OSCl的最前面一级反相器用或非门充当。当ctrl2为低电平时,OSCl正常工作;当ctrl2为高电平时,OSCl的输出恒为低电平,这样就实现了对OSCl的关断控制。

理想MOS模型中,栅-源电压等于或小于阈值电压时,器件中无电流。实际上,当Vgs接近VTH时栅极和衬底之间会产生弱反型层,并有一定的源漏电流,与Vgs呈指数关系,这种效应称为亚阈值导电。当Vds大于200 mV左右时,这一效应可表示为:

式中,VTH=kT/q;ζ>l,为非理想因子。

在低压电路中,因为MOS器件不能理想导通而工作于饱和区,所以亚阈值导电的特性得到广泛应用。振荡器OSCl内部反相器在Vdd=0.8 V时,由于|Vgs5|略小于|VTHP5|,VMps工作在亚阈值区,ID5很小,通过电流源的镜像作用,ID6=nID5。选择较大的n值,增大VMn4负载,实现输入到输出的反相功能。0SC2采用普通的CMOS反相器构成。同样加入RC延迟环节。使得振荡频率可控。

2.2 反馈控制电路

如前所述,反馈控制电路输出2个逻辑相反的控制信号,用于选择功率管的控制信号。反馈控制电路如图3所示,其中,Vfb是由电阻R1和VMn4对Vdd分压得到的,可近似为:

在电路启动阶段,VMn4截止,Ron4→+∞,Vfb输出高电平,ctrl1经过5级反相器输出为低电平,ctrl2为高电平,此时高电平

启动 电路 转换器 升压 电压 DC-DC 输入 电源 相关文章:

- 软启动抑制开关电源浪涌的原理及注意(12-07)

- UCC2870 启动性能分析(12-06)

- 汽车继电器启动机的原理作用图(12-05)

- 源于资深工程师的汽车启动/停止系统电源方案(01-15)

- 微型电机电源的设计(08-28)

- 用软启动禁止低成本输出来遏制电流尖峰(03-25)