基于AD6620的数字下变频(DDC)的频率变换器

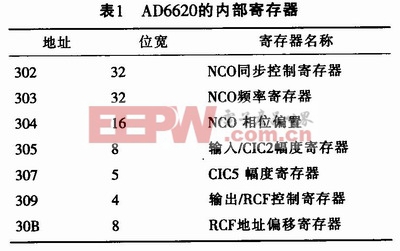

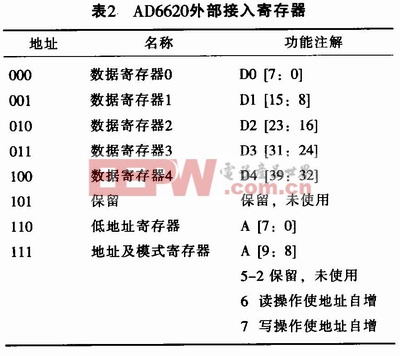

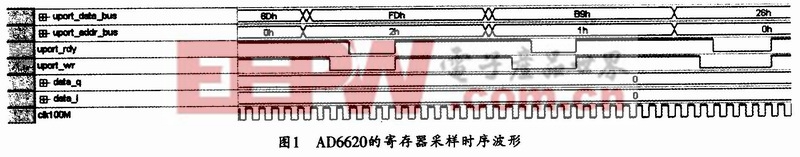

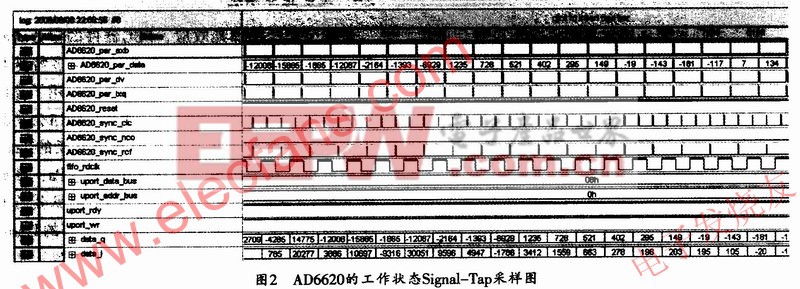

理多路下变频的复杂系统。只有一片AD6620工作在主控模式。 这两种模式的区别在于主控模式。在数据处理的每一级工作完成后,会发出一个同步脉冲,以用于复杂系统多个AD6620之间的同步工作。与此对应。从控模式的各级处理模块只有在接到这个脉冲后,才能开始本级的处理,这样才能以保证与其他AD6620芯片的工作协调。如主控模式二阶梳状滤波器CIC2完成其工作后,会向其他AD6620的SYNIC CIC2发出一个时钟周期的脉冲信号以用于同步。由于接收机中只使用了一片AD6620,而无需等待其他芯片协同工作的同步脉冲,故配置为模式0,即主控模式。 AD6620的控制接口分串行输入和并行输入两种。由于使用FPGA做芯片配置逻辑,所以,本文选用较灵活、效率较高的并行数据作为配置接口的逻辑输入。 AD6620内部各个模块的配置寄存器并不是等位长的。具体各模块内部配置寄存器的位长见表l所列,而内部寄存器的访问则必须通过外部接口寄存器来指定地址,并由高位到低位按字节写入。 外部接口寄存器的位长是固定的,按000到lll编址总共八个。其中低5位的5个寄存器是数据寄存器,可用于放入内部某地址的不定长数据。而高两位的两个寄存器是地址寄存器,用于存放将要访问的内部寄存器的目标地址,其中最高位111寄存器又和模式控制寄存器复用,且其最高两位标识为写增长和读增长,具体结构如表2所列。 在写寄存器的过程中,读信号要保持高(失效)。RDY信号是AD6620给出的握手信号,它会在写信号WR有效之后变低,之后,根据目标寄存器的不同,将在写信号有效后最早3个周期内再次升高,以表明写入工作完成。 与写寄存器过程相似,在读寄存器过程中,写信号也要保持高(失效),RDY信号是AD6620给出的握手信号,它会在读信号RD有效之后变低,之后再根据目标寄存器的不同,在读信号有效后3个周期到5个周期内再次升高,以表明写入工作完成。有效数据会在第N+2个时钟周期后稳定的保持在数据总线上。 为了使用FPGA来实现对AD6620的配置,在FPGA配置了一个FIFO以用于存放需要配置的所有寄存器的值。在RDY信号重新处于等待状态时读取该FIFO,可获得下一个目标寄存器的地址和寄存器内的数据。 设计时可用QUARTUS II自带的嵌入式逻辑分析仪SIGNAL-TAP来调试时序,以完成配置,图1所示是一个完整的寄存器写周期的各信号线采样时序波形。 配置成功后的AD6620工作情况如图2所示,从图2中可以看到AD6620的输入数据和AD6620的I,Q两路的数据输出,同时也可以观察到各级同步信号的脉冲波形。 6 结束语 本文对新型ADC器件AD6620使用中的重点和难点问题,也就是AD6620的配置问题,给出了其实现方法,该方法具有一定的参考价值。事实上。该方法中的所有配置均已通过FPGA仿真验证。并在工作过程中按照实际运行情况通过了Signal-TapII测试。

频率 变换器 DDC 变频 AD6620 数字 基于 相关文章:

- 实际环境应用中频率步进雷达系统的仿真与测试(12-12)

- 基于LONWORKS的智能频率采集节点设计(12-09)

- 一种以AVR单片机为核心的工频电压/频率仪设计(12-09)

- 如何用频率计算法设计RCC式开关电源?(12-08)

- 相位噪声对频率步进雷达的影响仿真(12-05)

- 在建筑自动化系统内节省能源的应用方案(04-23)