一种Flyback软开关实现方法

摘要:提出了一种Flyback电路ZVS软开关实现方法,即通过附加一个绕组,使激磁电感电流反向,从而来创造Flyback电路主开关的ZVS软开关条件;分析了其工作原理及电路参数的设计;最后的实验结果验证了该电路的工作原理及有效性。

关键词:Flyback电路;软开关;辅助绕组

0 引言

轻小化是目前电源产品追求的目标。而提高开关频率可以减小电感、电容等元件的体积。但是,开关频率提高的瓶颈是开关器件的开关损耗。于是软开关技术就应运而生。

本文提出了一种带辅助绕组的Flyback零电压软开关实现方法。通过对该电路的工作原理分析及实验的结果,验证了该电路的可行性。

1 工作原理

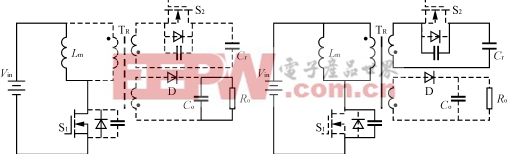

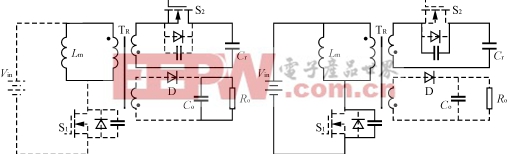

图1所示的即为本文所提出的软开关电路,辅助绕组的匝数与输出绕组相同。开关管S1与S2互补导通,之间有一定的死区防止共态导通,如图2所示。电路中激磁电感Lm的取值较小,使电流iLm可以反向以达到主开关S1的ZVS软开关条件,如图2(a)及图2(b)中iLm波形所示。由于电路在轻载及满载时的工作状况有略微不同,下文将具体分析电路轻载时的工作原理,满载时的工作原理将简要说明。考虑到开关的结电容以及死区时间,电路轻载时一个周期可以分为7个阶段,其各个阶段的等效电路如图3所示。其工作原理描述如下。

图1 带辅助绕组的flyback变换器

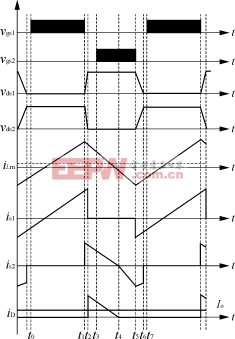

(a)轻载时的电路工作波形

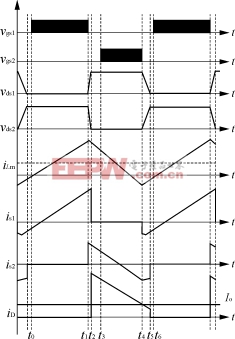

(b)满载时的电路工作波形

图2 电路主要工作波形

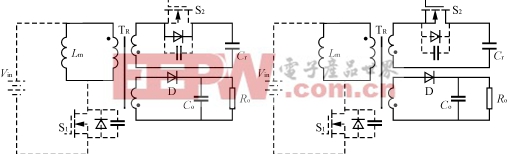

(a)Stage1[t0,t1] (b)Stage2[t1,t2]

(c)Stage3[t2,t3] (d)Stage4[t3,t4]

(e)Stage5[t4,t5] (f)Stage6[t5,t6]

(g)Stage7[t6,t7]

图3 各阶段等效电路图

1)阶段1〔t0,t1〕 该阶段S1导通,Lm承受输入电压,激磁电流iLm正向线性增加,从负值变为正值。在t1时刻S1关断,iLm达到最大值,该阶段结束。

2)阶段2〔t1,t2〕 S1关断后,激磁电感电流开始下降,其中一部分对S1的输出结电容充电,S1的漏源电压线性上升;同时另一部分通过变压器耦合到副边使S2的输出结电容放电,S2的漏源电压可以近似认为线性下降,t2时刻S2的漏源电压下降到零,该阶段结束。

3)阶段3〔t2,t3〕 当S2的漏源电压下降到零之后,S2的寄生二极管就导通,将S2的漏源电压箝位在零电压状态,也就是为S2的零电压导通创造了条件。同时二极管D也导通。

4)阶段4〔t3,t4〕 t3时刻S2的门极变为高电平,S2零电压开通。激磁电感Lm承受反向电压nVo(n为变压器原副边匝数比),Lm上电流线性下降,t4时刻下降到零,通过开关管S2及二极管D的电流也同时下降到零,该阶段结束。

5)阶段5〔t4,t5〕 通过二极管D的电流下降到零以后,二极管D自然关断。而S2继续导通,Lm上承受电压nVo,流过Lm的电流从零开始反向线性增加。t5时刻S2关断,该阶段结束。

6)阶段6〔t5,t6〕 此时激磁电感Lm上的电流方向为负,此电流一部分使S1的输出结电容放电,使S1的漏源电压可以近似认为线性下降;同时另一部分通过变压器耦合到副边对S2的输出结电容充电,使S2的漏源电压线性上升。t6时刻S1的漏源电压下降到零,该阶段结束。

7)阶段7〔t6,t7〕 当S1的漏源电压下降到零之后,S1的寄生二极管导通,将S1的漏源电压箝在零电压状态,也就为S1的零电压导通创造了条件。t7时刻接着S1在零电压条件下导通,进入下一个周期。可以看到,两个开关S1和S2都实现了软开关。

以上分析的是电路轻载时的工作原理,电路满载时的工作原理与轻载时略有差别,即不存在二极管D电流下降到零自然关断的环节,二极管D的电流在开关管S2关断以后才逐步下降到零,如图2(b)所示。

2 软开关参数设计

这里软开关的参数设计主要是变压器激磁电感的设计。

激磁电感电流的峰峰值可以表示为

ΔILm=(VinDT)/Lm (1)

式中:D为占空比;

T为开关周期。

则激磁电感电流的最大值和最小值可以表示为:

ILmmax=(VinDT)/2Lm+Io/n(2)

ILmmin=(VinDT)/2Lm-Io/n(3)

式中:Io是负载电流。

从上面的原理分析中可以看到S1的软开关条件是由|ILmmin|使S1的输出结电容放电,同时通过变压器对S2的输出结电容充电来创造的;而S2的软开关条件是由|ILmmax|对S1的输出结电容充电,同时通过变压器使S2的输出结电容放电来创造的。

S1及S2的软开关极限条件为储存在Lm上的能量对S1和S2的输出结电容充放电,足以令其中一结电容放电到零,而另一结电容充电到最大。

这样S1的极限条件为

(nVo+Vin)2(=)

(nVo+Vin)2(=)![]() Lm

Lm![]() (4)

(4)

S2的极限条件为

(nVo+Vin)2(=)

(nVo+Vin)2(=)![]() Lm

Lm![]() (5)

(5)

式中:C1,C2分别为S1和S2的输出结电容。

由于在实际电路中死区时间比较小,因此

- 详解几种可有效开关电源的电磁干扰抑制方法(01-23)

- 技术知识小贴士:二极管的识别技巧和检测方法(01-21)

- PCB板图的设计方法以及要点详细分析(01-17)

- 一种打破教科书上的按键检测方法(01-16)

- 工程师推荐:详解各种IGBT驱动电路和保护方法(12-25)

- 电源模块均流的基本原理、实现方法及仿真应用(12-24)