L波段频率源设计

0 引言

频率合成器是以一个高精确度和高稳定的石英晶体振荡器为基准参考频率,通过加、减、乘、除四则运算,获得与石英晶体振荡器同样精确度和稳定度的频率源。本文利用频率合成技术实现频率倍频,输出L波段点频源。

利用非线性电路产生高次谐波或者利用频率控制电路都可以构成倍频器。也可以由锁相倍频电路实现,该电路是一个闭环频率反馈系统,它主要由鉴相器、环路滤波器、压控振荡器和累加计数器构成,本设计采用这种方案。

目前出现了众多单片集成频率合成芯片,如美国QualComm公司的Q3236等,这种带有前置分频器和多个计数器的芯片,给锁相环电路的设计带来了极大的方便,为实现电路的小型化提供了可能。下面对总体方案设计,Q3236芯片的功能,电路和环路滤波器设计逐一讨论。

1 方案设计

本设计采用对晶体振荡器输出的参考信号,直接锁相倍频获得高频信号,再将高频信号放大到设计要求的方案。利用的是锁相频率合成技术,属于间接频率合成。整个倍频源基本由锁相倍频电路、放大和滤波电路组成,最重要的是锁相倍频电路。

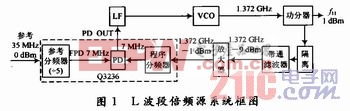

锁相倍频电路利用锁相技术实现频率合成,锁相环(PLL)是其中的重要组成部分,实质上是一个相位负反馈自动控制系统。基本由鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三部分组成。鉴相器用于比较两个输入信号相位,产生对应于两个信号瞬时相差的误差电压;环路滤波器具有低通作用,把鉴相器输出的误差电压滤波,滤除高频成分和噪声,以保证环路所要求的性能,提高系统稳定性;压控振荡器受误差电压控制,使得VCO的输出频率向参考频率靠近,直到消除频差而锁定。倍频源框图如图1所示。

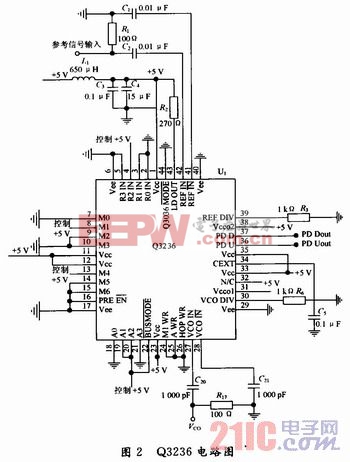

设计采用QualComm公司的高性能数字锁相环芯片Q3236,其内部集成有分频器、鉴相器和计数器。鉴相器在7 MHz频率上进行鉴相,可以提高鉴相灵敏度、缩短跳频时间。

2 硬件电路设计

2.1 锁相环的选择与使用

QualComm公司的Q3236是一种可在高达2 GHz频段工作的分频次数可编程的数字锁相环芯片,在正常工作状态下其功耗小于0.6 W,工作电压为5 V。其鉴相频率可达到100 MHz,本设计鉴相器工作在7 MHz,可应用于此项设计中。

Q3236主要电路性能为:

(1)双模前置分频器(10分频或11分频);

(2)9位M和4位A吞脉冲计数器,6位R参考分频器;

(3)100 MHz数字鉴频/鉴相器,鉴相灵敏度为320 mV/rad;

(4)单电源+5 V供电,功耗小于0.6 W;

(5)具有宽的输入灵敏度范围,从-10~+3.5 dBm。

Q3236数字处理器接口有三种工作模式:直接并行输入模式、串行总线模式和8位总线模式。因为设计的是输出固定频率的倍频源,不用跳频,于是采用直接并行输入模式,可以简化设计。设置 ‘HIGH’,Q3036

‘HIGH’,Q3036 ='LOW',6位R参考分频器的R4,R5不用,9位M计数器的M7,M5不用,R分频器和M计数器直接由外部输入。

='LOW',6位R参考分频器的R4,R5不用,9位M计数器的M7,M5不用,R分频器和M计数器直接由外部输入。

Q3236可提供的程序分频器分频比:对直接并行模式,当小于300 MHz时,为2~128;当小于2 GHz,为90~1 295。对外接的晶振,可提供的参考分频比为:直接并行模式1~16。

Q3236有加前置分频器和非预分频两种工作状态。工作在非预分频状态时VCO输出频率最高可达300 MHz,在前置分频器状态时VCO输出频率最高可达2.0 GHz。因为频率源输出1372 MHz,所以设计采用前置分频器、直接并行输入模式。参考分频器分频比编程只使用R0~R3位。 Fref/FPD=R+1;即35 MHz/7 MHz=5,对参考输入信号35 MHz进行5分频,所以R=4。R0,R1=“Low”,R2=“High”,R3=“Low”。压控振荡器输出的高频信号1 372 MHz利用M和A计数器进行N分频,N=Fvco/FPD=10*(M+1)+A,A≤M+1,M≠0。

Q3236具体电路图如图2所示。

2.2 环路滤波器设计

锁相倍频源的核心部分是环路滤波器的设计,因为环路滤波器的传输函数直接决定了整个环路的传输函数。从而在很大程度上决定了环路的噪声性能、稳定性、捕获和跟踪性能等。Q3236需要外接环路滤波器和压控振荡器才能构成一个完整的频率综合器。

常用的环路滤波器是一个线性低通滤波器,它可以滤除误差电压中的高频分量和噪声。常用的有RC积分滤波器、无源比例积分滤波器和有源比例积分滤波器。由传递函数可知,有源比例积分滤波器具有两个独立可调整的参数,并且具有滞后一超前特性,有利于环路稳定,于是本设计利用低噪声运放OP27及R,C元件组成一阶有源比例低通滤波器实现,主要参数是环路带宽和相位裕量等。

(1)环路带宽

环路带宽(Fn)是指开环传递函数幅度等于1时的频率,是环路滤波器设计的关键指标。如果锁相环的抖动主要由外部信号噪声引起,那么环路带宽应该越窄越好,这样可以抑制外部信号噪声,尤其是参考信号中的噪声;如果需要有效抑制压控振荡器的噪声,并且获得良好的跟踪和捕获性能,环路带宽应越宽越好。需要折中考虑,环路带宽一般取跳频间隔的1/60,鉴相器跳频间隔7 MHz,所以Fn=100 kHz,硬件调试时可以根据需要调整。

(2)相位裕量

相位裕量(φc)是指在开环传递函数幅度等于1时的相位相加180°的和。它与系统稳定性有关,相位裕量选择越低,系统越不稳定,相位裕量选择越大,系统越稳定,但系统的阻尼振荡越小,即以增加锁定时间为代价。要考虑适合的相位裕量,一般是40~55°之间,最优选相位裕量φc=45°。

为了将环路性能调到最佳,R1/2和电阻R2可选用相应阻值的电位器。环路滤波器电路图如图3所示。采用频率补偿技术,在放大器外部增加一个补偿极点,由R1,Cc组成低通实现,在保证一定增益裕度或相位裕度的前提下获得较大的环路增益。电阻R1分开成两个R1/2,避免相位检测出现电压偏差。

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)