基于EMCCD的驱动电路设计

2.2.1 Iφ,Sφ,Rφ驱动设计

在设计Iφ,Sφ以及Rφ驱动电路时,统一采用Elantec半导体公司的EL7457。它是高速四通道CMOS驱动器,能工作在40MHz,并提供2 A的峰值驱动能力,以及超低的等效阻抗(3 Ω),它具有3态输出,并通过OE控制,这对于CCD的驱动来说,容易实现灵活的电源管理。为了简化设计,固定Rφ2HV的电压幅值为典型值。在组成Iφ和Sφ的驱动电路时必须考虑CCD97驱动端的等效电容和电阻,如表2所示。

电路的时间常数:

又因为上升时间与时间常数的关系为:

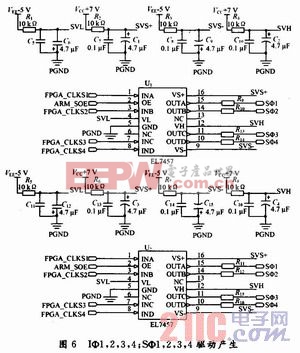

为了满足最佳上升时间(200 ns)的要求,必须在EL7457驱动输出端串上一个小电阻,原理如图6所示。

图6中,FPGA_CLKI1,FPGA_CLKI2,FPGA_CLKI3,FPGA_CLKI4为FPGA产生的TTL时序。ARM_IOE为ARM核产生的门控信号,用来控制驱动脉冲Iφ1,2,3,4的开关。由于理论与实际计算的误差,输出串接电阻R9,R10,R13,R14将通过硬件调试过程确定,以产生驱动CC97工作的最佳波形。同理,FPGA_CLKS1,FPGA_CLKS2,FPGA_CLKS3,FPGA_CLKS4为FPGA产生的TTL时序。ARM_SOE为ARM产生的门控信号,输出串接电阻待定。

在Rφ1,2,3产生电路中,因为其电压摆幅要求为0~12 V,故给它加以12 V的电源(见图7)。

它的驱动频率为11 MHz,输出的上升时间不需要串接电阻调节,可达10 ns。同理,FPGA_CLKR1,FP-GA_CLKR2,FPGA_CLKR3为FPGA产生的10 MHz的驱动时序,ARM_ROE为ARM产生的门控信号。这里还产生了一路控制行数据丢弃DG(Dump Gate)门控信号。该信号的摆幅同Rφ1,2,3。以上电路的连接均通过Multisim仿真,仿真波形如图8、图9所示。

2.2.2 Rφ2HV高压倍增驱动设计

Rφ2HV的幅值决定着倍增倍数,是EMCCD的一项重要可调参数,必须在指定范围内可调以满足不同场合的应用。在设计Rφ2HV时,由于其驱动电压摆幅高,现有的专用驱动芯片不能满足其高压驱动要求,必须采用特殊方法实现。根据E2V的文档,Rφ2HV的波形即可以是正弦波,也可以是方波。如果为方波,则其高电平要先于Rφ1变高,如果为正弦波,则要求其波峰要在Rφ1下降时到达。

如果采用方波脉冲,因为Rφ2HV为11 MHz,根据计算,其系统值将达2 W,CCD97上的功耗也将达到1 W;如果采用正弦波形式,可使CCD97上的功耗降到100 mW。在此,采用正弦波方式产生Rφ2HV。

周期矩形脉冲信号用傅里叶级数展开后,除了基波外,只有奇次谐波,在通过一个低通滤波器后,便能转化成正弦波。因为FPGA只能产生TTL时序,这里通过先将TTL的方波转化成正弦波,即可通过一个7阶的巴特沃斯滤波器,将20 MHz以后的高频分量衰减,保留基频。在得到10 MHz的正弦信号后,通过第一级放大,这里采用National Semiconductor公司生产的LM6172来构成。LM6172为双通道高速、低失真、低功耗的电压反馈型放大器。通过将LM6172的双放大器组合起来形成双端输入/双端输出以增加带负载能力。

在设计中,把基本的放大参数预设为使输入正弦信号放大到21 V,这样产生的双端信号经过一个初次级电阻,比为1:4的高频变换器达到输出高电平为45 V、低电平为4 V的驱动脉冲,供电电源为正负18 V的供电电源。为了使CCD97的增益可通过软件控制调节,这里使用了MAXIN公司生产的数字电位计MAX5429,预设目标是电压在40~50 V可调节。通过计算,反馈电阻参数如图10所示。其中,MAX5429为10 KB,其有32个可编程节点,上电后自动设置为节点16。在硬件电路设计完毕时,可通过ARM_RCS(片选信号),ARM_RUD(节点控制信号)来调节输出电压,如图10所示。这样通过对ARM的对应I/O口编程就能实现对CCD97的增益调节。但是因为这里选用了并联法,故调节时增益是非线性变化的。图11为正弦信号输入(经滤波器输出)经LM6172以及高频变换器后输出的仿真波形。

2.2.3 CCD97外围电路

CCD97除了需要外部的各种高摆幅转移脉冲,还需要各种幅值的控制信号输入。

在该系统中,为了简化设计,固定ABD(抗曝光),φRL、φRH high(视频信号复位端),DG high(行丢弃控制信号),DD(电源),OD(输出放大器电源开光),RD(复位上电电源)的值为典型值,分别为18 V,0 V,10 V.18 V,24 V,28 V,17 V。φRL,φRH的典型脉冲宽度为10ns,这里仍然采用EL7457来产生。信号OG为控制CCD97输出的门控信号,它同时控制两种模式的输出,而ODH,ODL分别为控制CCD模式和EMCCD模式放大器输出的电源开关。系统要求ODH和ODL可控,在需要时关闭,这样就要求通过模拟的开关来控制ODH,ODL的电压是+28 V还是接地。这里采用ADI公司的ADG453,它的VDD到GND端的输入电压可达32 V,模拟输入/输出值为VDD+2 V,达到这里控制ODH,ODL的通断要求(28 V)。其中CCD和EMCCD端口分别为该CCD的视频信号输出。其输出需要外接5 kΩ的负载。

3 结语

提出了一种新型的CCD驱动电路,不仅可以达到几十兆赫兹的驱动频率,而且编程方便,硬件电路简单,根据用户需求,只要更换晶振或适当修改程序就能实现特定目的,具有很强的灵活性。通过仿真及实验验证,该方法切实可行,性价比高,不仅适用于CCD驱动电路设计,对于其他需要多种逻辑信号的场合也同样适用。

- 分享:基于功放保护电路的设计分析与检测(12-09)

- 电源电路设计中常用测试仿真软件(12-09)

- 电路设计中主动PFC的优缺点分析(12-07)

- 开关电源电路设计的元器件选择(12-07)

- 10T真空电弧炉用40kA直流电源的研制与应用(12-07)

- GP02开关电源电路设计介绍(12-05)