增强电源设计中PFC段性能的方法

时间:04-22

来源:互联网

点击:

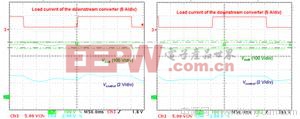

间的反馈电流,导致预期的控制信号(Vcontrol)放电。因此就没有观测到输出电压过冲。我们可进一步指明,启动时间未受明显影响。 图11 有Cfb(左图)及没有Cfb(右图)时的启动特性 图12显示了没有Cfb时(左图)及有Cfb时(右图)PFC段对突兀的负载改变(120W阶跃)的响应。我们的案例中(RfbU1=RfbU2),Cfb产生并不会相互抵消的额外极点及额外零点,且轻微改变环路特性。然而,最重要的是,采用Cfb还是改善了响应,因为较大的输出偏差(Output deviation)使这些负载阶跃类似于启动瞬态。因此,Cfb在这里同样帮助控制电路出现预料中的所期望的电平恢复。 图12 没有Cfb时(左图)及有Cfb时(右图)PFC段对负载阶跃变化的响应 结论 本文讨论了如何解决PFC段经常会面对的两个问题。首先,在CrM应用中,零电流检测在高输入线路时精度不高,而当输入线路电压非常接近输出电压时,可能会出现某些不需要的连续导电模式周期,导致一些功率因数退化,及可能出现一些人耳可听到的噪声。能够使用一颗简单的电阻来改善这功能。其次,在启动序列期间,PFC段也可能呈现出过大的过冲。可以在反馈感测网络中放置一颗电容来限制或抑制这过应力。即便是在电源设计的极晚阶段,这两种调整方法都易于实施。

增强电源设计 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)