一种改进的基于扫描的电路设计

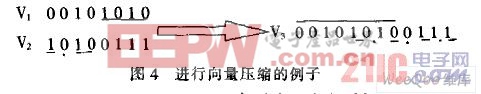

以发现,我们将要传入扫描链的测试向量,已经部分地包含在已经传入的测试向量序列中了,如图4所示。V1向量的后半部分刚好等于V2向量的前半部分“1010”,如果在传输向量的时候,先传输V1再传输V2,那么我们就只需要将V2的后半段向量信息传入扫描链就可以让V2原本的信息在扫描链中完整地呈现,如图中V3所示。很明显,我们原来要输入的测试向量的长度为16位,压缩后只有12位,节省了V2的前半部分传入扫描链的时间,从而减少了测试的时间,而且测试信息也没有减少,不会影响故障覆盖率。

3.2 用TEST—Per-Clock来缩短测试时间

我们对造成测试时间不够理想的原因进行分析:

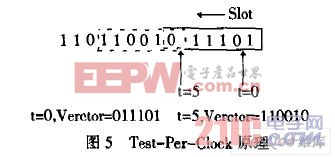

传统的基于扫描的测试电路是采取TEST—Per—Scan的方式来进行测试的,也就是说要先将测试向量扫描到电路内的由扫描寄存器所组成的扫描链内。然后才可以完成一次测试;将测试向量扫描到待测电路这个步骤是一位一位地进行的,所以如果一个电路需要长度较大的测试的向量时,那么在这整个测试过程里。将会花很多的时间在将测试向量输入到扫描链的这个步骤上,从而增加了测试时间。这个结构的测试向量的产生是利用LFSR产生出的伪随机向量,并将其送入电路做测试。用LFSR产生测试向量会产生出许多没有作用的测试向量,而这些没有作用的测试向量又会产生大量多余的时间将其送入扫描链中,造成测试时间更严重的浪费。如果采用TEST—Per—Clock的方式做测试,在扫描链里原本的测试向量,在用一个时钟的时间移进来一位之后,扫描链所含的值即是测试向量,对待测电路而言,其实都是一个新的测试向量,而且也具有伪随机向量的特性,如果此测试向量是有效的,我们的测试时间就只用了一个时钟的时间,而如果此测试向量无效,原本测试到没有作用的测试向量时所需的付出的时间代价,由于用了新的测试向量填满整个扫描链所需的时间,减少到只需一个时钟移进一位的时间。

如图5所示,每个时钟周期。Slot会往左移动一位,即在Slot内产生一个新的测试向量,而Slot大小可以看成扫描链的大小。

不过,由于每个时钟都要作测试,所以每个时钟在测试后都会产生新的测试结果。传统的基于扫描的测试环境里,电路输出结果传送出来的同时也将新的测试传进扫描链里。

如果输出的向量只有一位就不会有这样的问题。

因为我们现在要产生一个新的测试向量所需要的时间只有一个时钟周期,所以时问刚刚好。但是一般而言,待测电路的输出向量都会超过一位。所以我们在观察电路输出结果这个步骤上就会有问题。为了解决这个问题,需要对传统的基于扫描的测试电路做些修改。在待测电路的输出部分,可以用MISR来取代原来的扫描链电路,也就是将输出送到MISR做特征分析,如图6所示。

但是由于电路越来越复杂,电路的主要输入与输出的个数就会很多,如果对这样的待测电路加测试电路,将会出现外加电路面积过大的问题。所以我们针对MISR的部分提出一个方法,使得因测试而增加得MISR可以尽量地缩小。

缩小MISR的大小最直接的想法是将主要输出经组合电路压缩变小,但是这样会使错误覆盖率降低,使测试向量变多,这些问题在文献中谈到了。造成错误覆盖率降低的原因是如果我们将有共同输入向量的两个主要输出通过组合电路合并的话。将可能会造成原本可以测试到的错误,在合并后就测试不到了,所以造成了错误覆盖率的降低。

为了避免这个情况的发生,我们在向量压缩的过程中。只有将没有共同输入向量的主要输出合并在一起,就不会有问题出现了。如图6所示,两个不同的待测电路的主要输出经过合并以后输出到MISR,这样用一个与门代替了一个寄存器以便减少面积,而错误覆盖率则因为两两合并的主要输出端都没有相同的主要输出资料,所以就没有错误覆盖率降低的问题存在,即原来可以被侦测到的错误,在经过主要输出端合并之后仍然可以被侦测到。

4 结论

经过改进后的基于扫描的测试架构,用向量压缩来减少测试时间,并且将TEST—Per-Scan的测试方式改成了TEST—Per-Clock的测试方式,加快了测试的速度。

- 分享:基于功放保护电路的设计分析与检测(12-09)

- 电源电路设计中常用测试仿真软件(12-09)

- 电路设计中主动PFC的优缺点分析(12-07)

- 开关电源电路设计的元器件选择(12-07)

- 10T真空电弧炉用40kA直流电源的研制与应用(12-07)

- GP02开关电源电路设计介绍(12-05)