一种基于二阶相位扰动的DDS杂散抑制新方法

摘要 介绍了DDS的基本原理及杂散来源,分析了相位截断杂散原因和普通相位扰动原理,并在此基础上提出一种改进的二阶相位扰动方法。文中对该方法做了推导和论证。研究发现,使用该方法对DDS杂散的抑制效果比普通相位扰动法更显著,可达到每相位位18 dB。最后,利用Matlab中的DSP Builder进行仿真,验证了方法的可行性。

关键词 DDS;相位截断;杂散抑制;相位扰动

1971年,美国学者J‘Tiemey、G Rader和B Gold提出了以全数字技术,从相位概念出发直接合成所需波形的一种新的频率合成原理。此技术随着近年来数字集成电路和微电子技术的发展而迅速发展,被广泛应用于电子系统中。然而,由于DDS数字化实现的固有特点,决定了其输出频谱杂散较大,因此,对于DDS杂散抑制的研究是必要的。

常见抑制DDS杂散的方法有ROM数据压缩技术,加扰动技术,DDS+PLL技术等。其中相位扰动是一种常用方法,其基本思想是通过加入随机的扰动信号打乱误差序列的周期性,使由误差序列周期性引起的杂散分量变为幅度较低的相位噪声,从而改善DDS输出频谱的杂散特性。文中提出了一种新的相位扰动方法,其扰动信号由两个独立的同分布随机序列相加产生,这样能更有效地打乱误差序列的周期性,使杂散幅度降低。理论分析和仿真结果表明,这是一种有效的杂散抑制设计方法。

1 DDS基本原理及杂散分析

1.1 DDS基本原理

DDS即为直接查找存储表得到每个相位所对应输出波形的幅度值,通过改变采样频率和相位步进来改变输出频率,其原理结构如图1所示。

在图1中,相位累加器在时钟频率fc的控制下以步长K作累加,输出N位的量化相位序列,之后取其高W位作为ROM的寻址地址,对查询表ROM进行寻址,寻址输出的L位离散幅度序列经DAC转换成阶梯波,再经过低通滤波器(LPF)平滑后即可得到合成的信号波形。输出频率 。

。

1.2 杂散分析

DDS的工作原理决定了其输出杂散丰富,其中主要的杂散来源有3个方面:(1)相位截断误差εp(n),采用N位相位累加器的高W位寻址,截去低B=N-W位。由此引入了相位截断误差。(2)幅度量化误差εA(n),ROM中存储的正弦值是用有限的L位表示,这就产生了幅度量化误差。(3)DAC转换误差εDA(n),由实际DAC器件的非理想特性引起。

在DDS杂散的3个来源中,相位截断和DAC转换的影响最大,但目前DAC转换引起的杂散模型尚不能建立,所以在假设其他两个杂散源不存在的情况下,主要研究由相位截断引入的杂散。在无相位截断时可以得到ROM表输出序列S(n)。

可以看到,这时DDS输出的数字谱中除了所希望的信号外,还有εp(n)经余弦信号调制后的杂散成分。由文献中的推导知,相位截断情况下DDS的输出信噪比满足

从式(4)可以看出截断位数B每减少1位,杂散改善约6dB。

2 抑制杂散的相位扰动法

2.1 普通相位扰动原理

普通相位扰动技术是在每个时钟脉冲到来后,通过给相位累加器的输出加入满足一定统计特性的随机信号以打破误差序列的周期性,从而降低杂散,其原理如图2所示。

在图2中,N位的相位序列φ(n)与B位的扰动序列Z(n)相加后,通过相位截断为W位。相位截断过程可以视为量化间隔为△=2-w的量化过程,截断后的输出信号为φ(n)+Z(n)+ep(n),ep(n)为相位量化误差,总的量化噪声ε(n)=Z(n)+ep(n)是扰动信号与相位量化误差之和。由文献的扰动量化方法知,Z(n)和ep(n)都为在[-△/2,△/2]服从均匀分布的白噪声,它们的和ε(n)与φ(n)不相关,且为白色。因而这种加入的扰动序列,可使量化误差与原始输入信号独立,成为服从均匀分布的白噪声。

由上述分析知,加入扰动信号的DDS输出信号X(n)=sin(2π(φ(n)+ε(n))),假设,上式在2πfn处用泰勒级数展开有

采用普通相位扰动法,可以使杂散分量的抑制从每相位位6 dB增加到12dB。

2.2 改进的二阶相位扰动法

二阶相位扰动法在研究普通相位扰动法的基础上形成,该方法中,扰动序列是由两个独立同分布的随机序列相加产生。具体的原理结构,如图3所示。

如图3所示,两个B位独立同分布的随机序列相加生成B+1位的扰动序列,然后由B+1位的扰动序列扰动原始输出φ(n),这样能获得更好的杂散抑制效果。

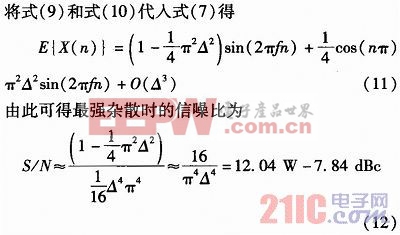

对于二阶相位扰动,需要考虑量化噪声的三阶矩成分E{ε3(n)},此时的输出信号泰勒级数展开式为

假设扰动序列为在[0,△]上服从均匀分布的两随机序列之和,则扰动序列的概率密度为

将满足式(14)的扰动序列加在相位序列上,并且截断为W位,由此产生的总量化噪声有3种情况

从式(17)可知,采用二阶相位扰动法,杂散分量的抑制可达每相位位18 dB,相比普通相位扰动法性能有很大改善。

3 仿真验证

利用嵌入到Matlab中的DSP Builder工具进行仿真,具体的模型如图4所示。仿真参数:时钟频率fc=1 MHz;频率控制字K=485 952;相位累加器位数N=22;相位寻址位数W=4;ROM输出位数L=20;取两个独立的24级18位输出m序列之和作为扰动序列。仿真结果送到Matlab的工作空间并进行功率谱变换,从而验证系统的设计。

- 软启动抑制开关电源浪涌的原理及注意(12-07)

- 抑制开关电源电磁干扰设计要点及方法(12-07)

- 用LYTSwitch-0设计出适用于全球所有国家和地区的灯泡(02-13)

- 抑制同步开关噪声的超带宽电磁带隙结构研究(02-02)

- 一种浪涌抑制模块在开关电源设计中的应用方案(01-23)

- 详解几种可有效开关电源的电磁干扰抑制方法(01-23)