TI案例:多媒体处理器动态电源管理

多媒体处理器通常是便携式电子设备中功耗最高的器件。降低 CPU 功耗要求的常见方法是降低时钟频率或工作电压,但是一般而言这样做会使系统性能降低。另一方面,芯片设计人员还提出了各种片上方法来降低功耗,并且不会对系统产生不利影响。本文介绍了这些方法的概念,以及我们如何运用它们实现节能的目的,同时还讨论了帮助处理器芯片获益的一些外部电源管理器件和电源 IC。

有源电源管理

片上电源管理技术主要适用于两类应用:管理有源系统功耗和管理待机功耗。

有源电源管理分为三个部分:动态电压与频率缩放 (DVFS);自适应电压缩放 (AVS);以及动态电源转换 (DPS)。另一方面,静态功耗管理包括在需要进行更多处理以前将空闲系统维持在一种低功耗状态。这种电源管理使用所谓的静态漏电管理 (SLM),其通常利用从待机到关机的数种低功耗模式。

让我们来看一下有源模式。利用 DVFS,根据应用所要求的不同性能,时钟频率和电压在软件中得到了降低。例如,一款包括了先进 RISC 机器 (ARM) 和数字信号处理器 (DSP) 的应用处理器,即使 ARM 组件可以运行在高达 600 MHz 的时钟频率下,但却并非总是需要所有这些计算能力。一般而言,软件会选择数个预定义处理器工作性能点 (OPP),其包括确保处理器能够运行在满足系统处理要求的最低频率下的电压。在对满足不同应用要求的功耗进行优化的过程中,为了获得更大的灵活性,人们为处理器中的互连和外设预定义了一个单独的器件内核 OPP 集。

与给定的 OPP 相对应,软件向外部稳压器发出控制信号来设置最低电压。例如,DVFS 适用于两个电压源 VDD1(为 DSP 和 ARM 处理器供电)和 VDD2(为子系统和外设之间的互连供电),同时这些电源轨提供芯片所需的大部分电量(一般约为全部所需电量的 75% 到 80%)。通过将 DSP 处理器转入一个 ARM 可以高达 125MHz 时钟频率运行的低工作性能点完成对 MP3 解码的同时,还可以有许多剩余电力用于完成其他任务。为了获得具有理想功耗的这种功能性,我们可以把 VDD1 降至 0.95V,而非保证 600 MHz 运行的 1.35V 最高电压。

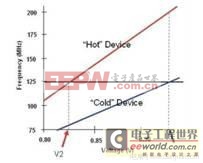

第二种有源电源管理技术即自适应电压缩放 (AVS) 基于芯片制造和器件工作寿命期间出现的各种变化。这种技术是相对于 DVFS 的,DVFS 中所有处理器均具有相同的预编程 OPP。正如人们认为的那样,在大多数现有制造工艺中规定频率要求的芯片性能符合一种充分定义的电源分配。相比许多“冷”器件,一些器件(即“热”器件)可以在较低的电压下达到规定频率。此时,AVS 便可以发挥作用了—处理器检测其自有性能水平,并相应地调节各电压源。专用片上 AVS 硬件可实施一个反馈环路,其并不要求处理器介入,从而动态地优化电压电平来应对处理结果、温度和硅芯片性能降低中的变化(请参见图 1)。

图1

图 1 显示了特定处理器的典型性能分布情况。其中,“冷”器件要求 0.94V 电压以实现 125 MHz 的运行,而“热”器件则只需要 0.83 V 就可实现相同频率的运行。自适应电压缩放 (AVS) 使用一个可相应调节电源电压的反馈环路,这样单个器件便可以完成特定处理任务所需的频率运行了。

运行中,软件为每一个 OPP 安排 AVS 硬件,同时控制算法通过一条 I2C 总线向外部稳压器发送命令,逐步递增降低相应稳压器的输出,直到该处理器刚好超出目标频率要求为止。

例如,开发人员可以在一个适合于所有情况的电压下并以 0.95V 的 125 MHz 频率为目标开始进行设计(上面图 1 所示的 V1)。但是,如果一个使用 AVS 的“热”器件被插入该系统,那么该片上反馈机制就会自动地将电压降至 ARM,即 0.85V 或更低(上面图 1 所示的 V2)。

前两种有源电源管理方法可获得理想速度下运行器件局部所需的最低工作电压。相比之下,第三种方法动态电源转换 (DPS) 可确定器件何时完成其当前计算任务,如果当前并不需要,则将器件切换到低功耗状态(请参见图 2)。例如,在等待 DMA 传输完成时,处理器进入低功耗状态。唤醒时,处理器可以在数微秒时间内迅速返回到正常状态。

图2

图2 动态电源转换 (DPS) 将完成任务后的特定器件的相应部分切换至低功耗状态。

无源电源管理

DPS 只能将多媒体片上系统 (SoC) 的某一部分切换至低功耗状态,而在许多情况下将整个器件都切换至低功耗状态是颇具现实意义的(无论是无应用程序运行时自动切换,还是根据用户要求切换)。为了达到这一目标,我们可以运用了静态漏电管理 (SLM),其被用于启动待机或关机模式。一个关键的区别在于,在待机模式下该器件可维持内部存储器和逻辑电路

分立器件 转换器 稳压器 数字电源 背光驱动 电源模块 电池管理 网络通信 消费电子 汽车电子 电源管理 相关文章:

- 基于TPS2393A实现大电流热插拔应用的设计方案(01-28)

- 基于一个基于分立器件的自动恒流充电电路设计(11-23)

- 新型流体电池技术可实现更廉价有效的能量存储(08-19)

- 针对便携式设备充电电路的分立器件保护方案(11-11)

- 延长UPS电源寿命的四大方法(05-27)

- 一款可替代集成 MOSFET 驱动器的卓越解决方案(04-18)