真相:准谐振反激的设计内幕

时间:09-12

来源:互联网

点击:

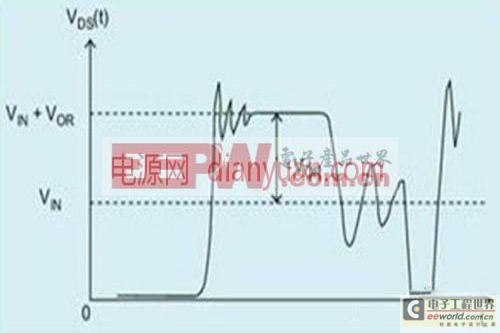

如果不用固定的时钟来初始化导通时间,而利用检测电路来有效地“感测”MOSFET (VDS) 漏源电压的第一个最小值或谷值,并仅在这时启动MOSFET导通时间,结果会是由于寄生电容被充电到最小电压,导通的电流尖峰将会最小化。这情况常被称为谷值开关 (Valley Switching) 或准谐振开关。这篇文章的目的目的在于和大家分享关于准谐振反激的原理、应用及参数计算方面的知识。

准谐振 QR

Q(Quasi)

R( resonant)

主要是降低MOSFET的开关损耗,而mos的开关损耗主要是来源于自身的输出电容。

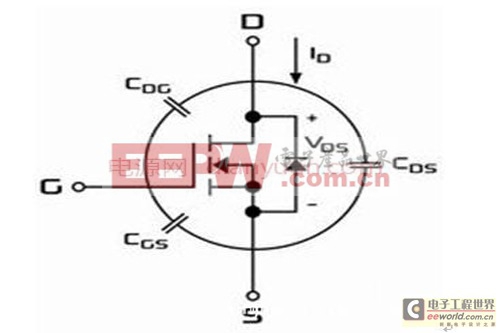

从上图中,大家可以讨论一下,一般的开关损耗来自于那几个部分的寄生电容产生的。在传统的非连续模式反激DCM)的停滞时间内,寄生电容将会跟VDC周围的主要电感产生振荡。寄生电容上的电压会随振荡而变化,但始终具有相当大的数值。当下一个周期MOSFET导通时间开始时,寄生电容会通过MOSFET放电,产生很大的电流尖峰。由于这个电流出现时MOSFET存在一个很大的电压,该电流尖峰因此会做成开关损耗。

从上面的图可以看到,准谐振跟一般的传统反激原理基本一样。

Lleak是初级漏感,Rp是初级电阻,Cp是谐振电容;

当副边绕组中的能量释放完毕之后(即变压器磁通完全复位),在开关管的漏极出现正弦波振荡电压,振荡频率由LP、CP决定,衰减因子由RP决定。

对于传统的反激式变换器,其工作频率是固定的,因此开关管再次导通有可能出现在振荡电压的任何位置(包括峰顶和谷底。

准谐振反激 相关文章:

- 基于UCC28600准谐振反激式开关电源的方案(12-08)

- 基于安森美NCP1937控制器的电源应用(12-02)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)