基于PCI9054的接口卡设计

PCI总线支持突发传送,多处理器和并发工作,广泛应用于各种平台设计。基于PCI9054的接口板也广泛地应用于各种高速、大数据量的处理系统。由于PCI9054桥接有PCI总线和本地总线,开发者不必过多考虑复杂的PCI总线规范,从而能有更多精力开发硬件和驱动程序设计。

这里以PCI9054为例,给出了接口板的硬件和软件设计,详细论述了该系统设计的原理图和用VHDL语言编写的部分逻辑源程序,以供相关开发人员参考。

1 PCI9054简介

PCI9054是PLX公司推出的一种32位33 MHz的PCI总线主控I/O加速器,它采用PLX在业界领先的数据流水线框架,包含DMA引擎,可编程的PCI起始器和目标数据传输模式以及PCI信息传输功能。遵循PCI2.2版规范,可获得最高可达132 MB/s的突发传输速度。它使复杂的PCI接口应用设计变得相对简单,目前已成为主流的PCI接口器件之一。

PCI9054数据传输有3种方式:主模式、从模式和DMA方式。其内部具有2个DMA数据通道,每个通道均支持块Scatter/Gather的DMA方式,双向数据通路上各有6个FIF0进行数据缓冲,可同时进行高速的数据接收和发送,8个32位Mailbox寄存器可为双向数据通路提供消息传送,PCI9054内部框图,如图1所示。

PCI9054的本地总线有M、C、J 3种工作模式,可通过模式选择引脚MODE[1:0]进行控制,其中C模式能够满足绝大多数的应用需求,而且C模式的本地总线操作时序最为简单,逻辑控制相对容易,其开发难度相对较低。C模式下PCI9054通过片内逻辑控制将PCI的地址线和数据线分开,很方便地为本地工作时序提供各种工作方式,一般较广泛应用于系统设计中。因此,如无特殊需求,建议采用C模式,这也是本接口卡所采用的模式,同时PCI9054的本地总线时钟可由外部提供,该时钟可和PCI时钟异步。

2 接口卡硬件设计

接口卡主要功能是:对外设装置进行工作模式和状态检测,控制端对检测结果进行相应的数据接收或发送操作。其工作流程是:由控制端提出请求,根据进入接口卡的信号对外部设备进行工作模式和状态检测并决定是否对进入外设的信号进行接收或发送。机械特性方面,接口卡遵从Eurocard工业标准,采用6U(233.35 mmxl60 mm)结构。接口卡的逻辑框图如图2所示。

由图2可知,接口卡分为3个部分:PCI总线接口、本地总线接口和串行EEPROM接口。

2.1 PCI9054与PCI总线接口

PCI9054与PCI总线接口的连接实际上是PCI9054与cPCI连接器Jl的连接,即PCI9054的PCI端信号线通过10Ω的端接电阻与PCI插槽的相应信号线对应连接。PCI总线接口信号包括地址数据复用信号线、接口控制信号线、中断信号线等。PCB设计时,为了满足反射条件,需注意PCI总线信号的布线及长度,普通信号长度,从连接器到PCI桥器件间距应不大于1.5英寸(3.81 cm),PCI_CLK信号布线长度为2.5±0.1英寸,否则会导致信号不稳定甚至总线冲突,无法开机。PCI9054内部有可编程的FIF0,实现零等待突发传输及本地总线与PCI总线之间的异步操作,本地总线时钟由外部提供,该时钟可以和PCI时钟(33 MHz)异步,本地总线选择工作在50 MHz,由频率为50 MHz的晶振OSCl产生,同时送往PCI9054本地端的时钟信号LCLK与送往CPLD的时钟信号CCLK要等长,以保持它们同步。

2.2 PCI9054与本地总线接口

本接口卡中的CPLD采用Xilinx公司生产的XC95288XL,实现对接口卡的逻辑控制。C模式下PCI9054通过片内逻辑控制将PCI的地址线和数据线分开,然后与CPLD相对应的引脚连接,能方便为本地工作时序提供各种工作方式,一般广泛应用于系统设计。

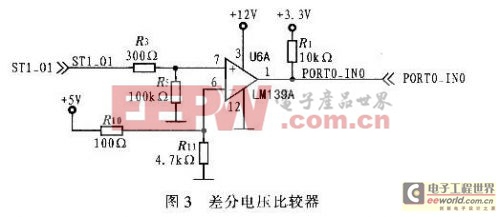

本地总线部分中的INPUT_BUFFER部分主要由差分电压比较器组成,如图3所示。当从J4进入的信号电压(引脚7)大于基准电压(引脚6)时,输出高电平(引脚1)并进入CPLD,控制器通过PCI9054读入。0UT_BUFFER部分主要是实现控制器对外设接收或发送数据的控制。

2.3 PCI9054与EEPROM接口

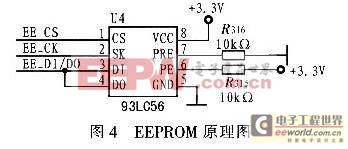

PCI9054提供4个引脚EEDI,EED0,EESK,EECS与串行EEPROM-93LC5*个引脚DI、D0、SK、CS相连,此外93LC56的VCC引脚需要接+3.3 V电源,GND接地。因为需要对串行EEPROM进行写操作,串行EEPROM需处于可编程而且非保护状态,所以PE通过10 kΩ的电阻上拉后接高电平3.3 V电压,而PRE通过10 kΩ的电阻下拉后接地。EEPROM原理图如图4所示。

连接好PCI9054与PCI总线接口、本地总线接口和串行EEPROM接口后,还需对寄存器进行配置,配置时需借助于Windriver工具,寄存器的配置包括PCI配置寄存器的配置、本地配置寄存器的配置及对EEPROM初始化。

配置PCI配置寄存器主要是填写生产商ID号、器件ID号、子系统生产商ID号和类码

- ARM和WinCE6.0下nRF24L01的驱动设计(05-28)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)