揭秘:如何提高开关电源待机效率

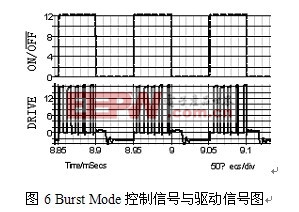

当处于轻载或待机条件时,由周期比PWM控制器时钟周期大的信号控制电路某一环节,使得PWM的输出脉冲周期性的有效或失效,如图6所示。这样即可实现恒定频率下通过减小开关次数,增大占空比来提高轻载和待机的效率。该信号可以加在反馈通道,PWM信号输出通道,PWM芯片的使能引脚(如LM2618,L6565)或者是芯片内部模块(如NCP1200,FSD200,L6565和TinySwitch系列芯片)。

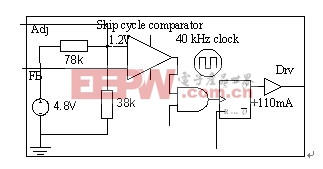

NCP1200的内部跳周期模块结构见图7,当反馈检测脚FB的电压低于1.2V(该值可编程)时,跳周期比较器控制Q触发器,使输出关闭若干时钟周期,也即跳过若干个周期,负载越轻,跳过的周期也越多。为免音频噪音,只有在峰值电流降至某个设定值时,跳周期模式才有效。

图7 NCP1200跳周期模块结构

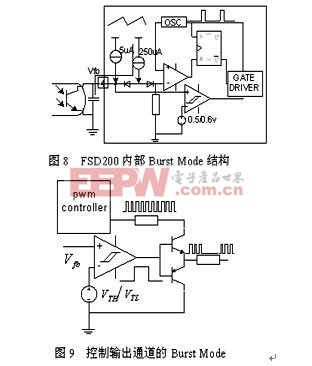

而FSD200则是通过控制内部驱动器实现可控脉冲模式,即将

脚的反馈电压与0.6V/0.5V迟滞比较器比较,由比较结果控制门极驱动输出,其结构可见图8。我们可根据此原理用分立元件实现普通芯片的Burst Mode功能,即检测次级电压判断电源是否处于待机状态,通过迟滞比较器,控制芯片输出,电路如图9所示。

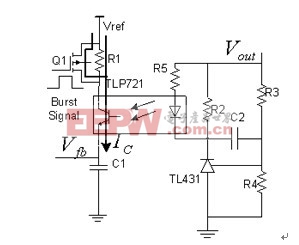

控制反馈通道是实现一般PWM控制器的可控脉冲模式的方法之一。其电路可见图10,

是

反馈信号,当Burst Signal为低电平时,Q1关断,

电路正常工作,当Burst Signal为低电平时,Q1导通,R1被短路,

流过Q1

被拉高至

-0.6V,反馈信号

不能反映在

上,控制器因此输出低电平。

另外对于有使能脚的PWM控制器,如L6565等,用可控脉冲信号控制使能脚使控制芯片有效或失效,也可以实现Burst Mode,上述Burst Signal可由图1中所示的迟滞比较器产生。

图10 控制反馈通道的Burst Mode

4 存在的问题

以上介绍的降频和Burst Mode方法在提高待机效率的同时,也带来一些问题,首先是频率降低导致输出电压纹波的增加,其次如果频率降至20kHz以内,可能有音频噪音。而在Burst Mode的OFF时期内,如果负载激增,输出电压会大大降低,如果输出电容不够大,电压甚至可能降低至零。如果增大输出电容,以减小输出电压纹波,则会导致成本增加,并会影响系统动态性能。因此必须综合考虑。

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)

- 高效地驱动LED(04-23)

- 开关电源要降低纹波主要要在三个方面下功夫(06-24)

- 超宽输入范围工业控制电源的设计(10-15)