时钟芯片的低功耗设计研究

然当阈值电压和工作电压一起减小时,电路的功耗显著降低,但由于阈值电压的值与工艺参数有关,当阈值电压减小到一定程度时,能量又随阈值电压的减小而增加。从上面分析中可以看出,在振荡电路工作电压的选择上,由于要考虑所采用的工艺以及器件的工作速度,因此不能一味地追求很低的工作电压,要对整个电路功能的实现做全面考虑。

振荡器的基本是Pierce模型。在工作电压较低的时候,要选择合理的宽长比W/L为满足阈值电压的要求,但由(4)式可知,宽长比W/L与工作电流ID成正比。宽长比W/L的增加,又带来了两方面问题,即工作电流ID的增大和管子尺寸增加。为了减小ID,在NMOS管和PMOS管两端应各接一个有源电阻(M2、M3)来对工作电流进行分流;另一方面,管子尺寸的增加,使得扩散电容和负载电容CL也增加了,这会导致电路充放电时间增加,引起额外功耗。因此,对宽长比W/L的选择是决定振荡电路功耗的一个关键参数。具体电路参见图2。

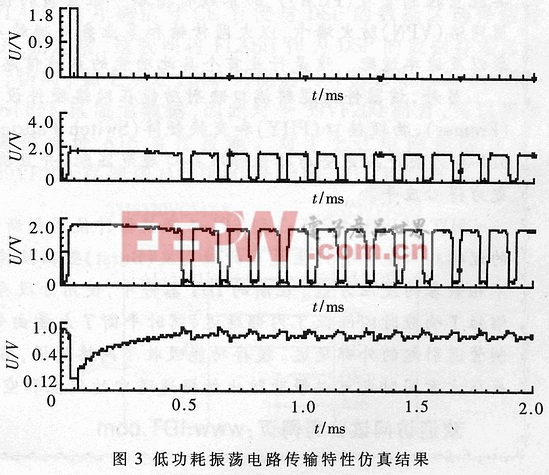

为了观察振荡电路的输出特性是否满足低功耗设计要求,用Spectres软件作了仿真。从图3的仿真结果可以看出,当V dd1=1.8V、晶振频率为32.768kHz时,输出满足系统要求。

2.2 分频电路低功耗设计

为了满足时钟模块的输入要求,采用多级分频电路对来自振荡电路的高频信号进行分频处理。由于分频电路的分频级数较多,而且每一级分频电路的工作频率是以倍数等比下降的,因此,因此分频电路工作电压的设计应用考虑各级之间的输入和输出的关系。可以将分频电路分为两部分,前三级为高频部分,采用较低的工作电压,然后加一个电平转换器,把 经过1:8分频后的输出电压提升到标准工作电压;后面部分为低频部分,包括12级分频电路,采用标准工作电压。这一部分分频电路可采用带复位的锁相环,以实现对时钟电路复位和测试的控制。

由于振荡电路和第一级分频电路的输入信号的频率为晶振频率,因此采用最低的工作电压V dd1,以期将功耗降下来;对于第二级和第三级,采用的工作电压V dd2比第一级略高;在第三级分频后加一个缓冲器和电平转换电路,采用的工作电压V dd3高于V dd2,即V dd1

前三级分频器电路由静态主从型D触发器和传输门组成,时钟信号通过传输门加到锁存器两端。前一级的输出为后一级的输入。通过Spectres软件对前三级分频器的输出特性进行仿真可知,当工作电压最低为2V左右时,仍能保持正常工作,满足低功耗设计要求。

综上所述,ASIC低功耗设计应从多层次设计上考虑降低功耗问题。首先应从CMOS电路的功耗为源探讨降低功耗的电路的体系结构,然后针对各个功耗较大的电路,逐个进行电路优化和参数改进,从而实现对工作在高频部分的电路的功耗进行控制,以满足整个芯片的低功耗设计要求。这种低功耗设计方法通过在低功耗时钟芯片上的设计得到很好的体现。经过实验和流片后测试,都验证了本文所提出的低功耗设计方案是可行的,不仅满足了高性能低功耗时钟芯片的设计要求,而且可以缩短设计周期。

- 可穿戴设备要流行,全方位高效电源管理是前提(12-09)

- 基于BQ25504的低功耗、增压型转换器的设计研究(12-09)

- 一款无Y电容原边调整的低功耗充电器设计(12-09)

- 超低功耗倾角测量仪的设计(12-09)

- 六大低功耗、高性能电源管理解决方案(12-08)

- 浅析低功耗多模式大功率电源制作步骤(12-05)