一种DC-DC升压型开关电源的低压启动方案

摘要:设计了一种DC-DC升压型开关电源的低压启动电路,该电路采用两个在不同电源电压范围内工作频率较稳定的振荡器电路,利用电压检测模块进行合理的切换,解决了低输入电压下电路无法正常工作的问题,并在0.5μm CMOS工艺库(VthN=0.72 V,VthP=-0.97 V)下仿真。仿真结果表明,在0.8 V低输入电压时,通过此升压型开关电源,可以将VDD升高至3.3 V。

关键词:开关电源;环形振荡器;低压启动;COMS

0 引言

各种便携式电子产品,如照相机、摄像机、手机、笔记本电脑、多媒体播放器等都需要DC-DC变换器等电源管理芯片。这类便携式设备一般使用电池供电,总能量有限,因此,电源芯片需要最大限度地降低工作电压,延长电池的使用寿命。传统DC-DC的工作电压一般都在1.0 V以上,本文所设计的电路将这一启动电压降低至0.8V。

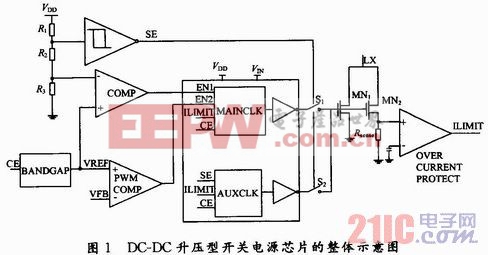

1 电路整体示意图

DC-DC升压型开关电源在低输入电压下工作,利用控制电路导通和关断功率管,在功率管导通时,电感储存能量;当功率管关断时,电感释放能量,对输出电容充电,输出电压升高。当输入电源低至1.0 V以下,如果DC-DC芯片的驱动电压取自输入电源,芯片内部电路就不能正常工作,DC-DC便无法启动;如果DC-DC芯片的驱动电压取自输出电压,同样,芯片根本无法启动及进行任何升压动作。本文针对输入电源电压变化范围较大,在考虑商业成本的情况下,设计了2个振荡器电路:主振荡器和辅助振荡器。辅助振荡器靠输入电压供电,0.8 V即能起振,在VDD升至1.9 V以前控制功率管的导通与关断,使VDD逐步抬升。主振荡器靠输出电压即VDD供电,在VDD升至1.9 V以后以一个较稳定的频率工作,抬升并维持输出电压。电路的整体示意图如图1所示。该电路包括主振荡器、辅助振荡器以及它们的切换电路、带隙基准电路、PWM比较器、过压保护电路、过流保护电路等。

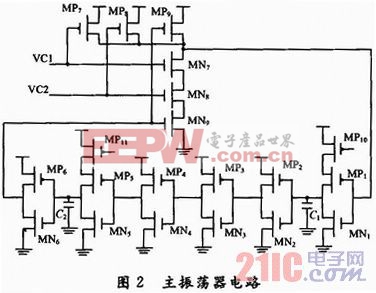

在构想了两个在两段不同的电源电压下工作的振荡器电路之后,就可以对两个振荡器电路分别进行设计。环形振荡器因其结构简单,易于集成,而用于许多集成电路芯片的设计,但其振荡频率受电源电压变化的影响较大,文献中所提出的方案虽然有较大改善,但它采用了大的集成电阻,这不仅增大了芯片面积,而且集成电阻阻值随工艺偏差很大,还会进一步增大环振输出频率的不稳定性。文献所提出的改进型环形振荡器电路频率稳定度高,适用于电源电压变化较大的集成电路系统,但它采用了耗尽型MOS管,增加了电路的成本,不利于商业开发。本文所设计的主振荡器采用如图2所示的环形振荡器结构。VC1,VC2分别为过压保护电路,PWM比较器的输出信号,MP10和MP11为带隙基准提供的镜像电流,合理的控制镜像电流和电容C1,C2的大小,即能够使主振荡器在1.9~8 V的VDD区间输出350 kHz左右较稳定的振荡频率。

3 辅助振荡器的设计

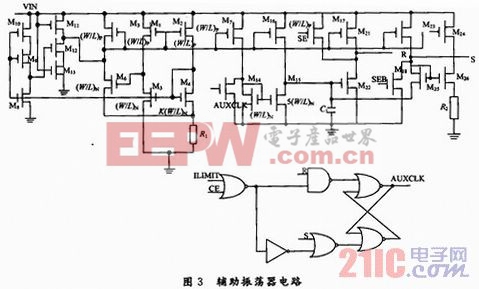

文献中提出的辅助振荡器电路也采用环形振荡器结构,它利用亚阈值导通的原理,使得起振电压降至0.8 V,但是这个辅助振荡器在0.8~1.9 V的VDD区间里频率变化很大,会在电路启动阶段造成很大的浪涌电流,造成系统的不稳定。

文献中提出的辅助振荡器克服了以上缺点,既保证了在0.8 V起振,又避免了振荡频率变化过大,但是,在辅助振荡器关断之后由于工艺偏差可能会在R,S端出现不确定状态,导致功耗过大,并造成后续电路不能正常工作。本文在文献的基础上加以改进,增加M17管,M18管,所设计的辅助振荡器如图3所示。

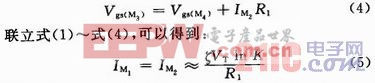

图3中,M1~M12是低输入电压偏置电流电路,这个电路的主要功能是在低输入电压下产生一个恒定的纳安级的偏置电流。这一不随电源电压变化的偏置电流将为图3所示的辅助振荡器提供偏置。M8~M13为启动电路,M3,M4都工作在亚阈值区,

式中:K=(W/L)M4/(W/L)M3,通过式(5)可以发现,偏置电流IM1,IM2与输入电源无关。

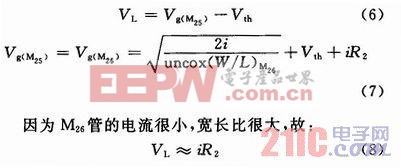

恒流源II和I4对电容C1充放电,该振荡器的核心模块是两个比较器,M21,M22组成COMP1,该比较器阈值较高,为M22管的导通阈值,记为VH=Vth。M22,M23,M24,M25,M26,R2组成COMP2,该比较器阈值较低,记为VL:

SE为辅助振荡器切换信号,SEB为SE的反信号。当VDD低于1.9 V时,SE为高电平,M17,M18都截止,不影响R,S触发器的翻转,辅助振荡器工作,开关S1断开,S2闭合;当VDD高于1.9 V时,SE为低电平,辅助振荡器关断,开关S1闭合,S2断开,M17,M18都导通,R=1,S=0,AUXCLK被锁定为高电平,既减小了功耗,也避免了辅助振荡器关断之后R,S端出现不确定状态。

4 电路整体仿真结果与分析

整体电路在0.5μm CMOS工艺库(VthN=0.72 V,VthP=-0.97 V)下仿真,仿真条件为VIN=0.8 V,仿真结果如图4所示。

启动 方案 低压 开关电源 DC-DC 升压 一种 相关文章:

- 软启动抑制开关电源浪涌的原理及注意(12-07)

- UCC2870 启动性能分析(12-06)

- 汽车继电器启动机的原理作用图(12-05)

- 源于资深工程师的汽车启动/停止系统电源方案(01-15)

- 微型电机电源的设计(08-28)

- 用软启动禁止低成本输出来遏制电流尖峰(03-25)