手机USB充电和过压保护设计方案

本文将重点结合手机侧的要求来分析USB充电和过压保护设计策略,以及相应的解决方案。

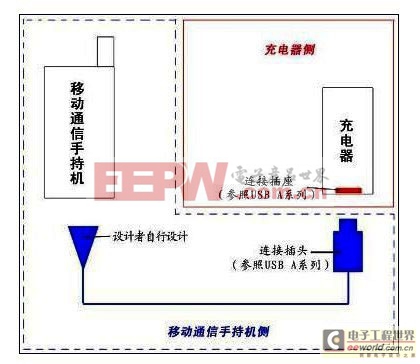

图1 YD/T 1591-2006 标准所涵盖手机侧和充电器侧两大部分

手机充电要求及不同充电电路解决方案比较

通常所称的手机充电器实际上是交流/直流(AC-DC)电源适配器,真正的充电电路乃是在手机内部。根据YD/T 1591标准要求,手机充电接口直流输入电压也就是充电器的输出电压为5 V±5%,即范围为4.75 V~5.25 V;标准充电器的充电电流为300 mA至1,800 mA,非标准充电器(如笔记本电脑的USB端口等)的最大充电电流为500 mA。无论充电器的输出功率如何,手持机侧充电控制电路应能根据自身需求实施安全充电,不应出现过热、燃烧、爆炸以及其它电路损坏的现象。

在手机内部的充电电路方面,业界有着不同的解决方案,主要包括分立式充电IC、集成式充电IC、电源管理集成电路(PMIC,或称电源管理单元,简称PMU)+外部充电功率元件等三种。这三种方案各有其特点。其中,对于分立式充电IC方案而言,优点在于便于增加或修改功能,从而更有利于实现产品差异化,此外,这种方案有利于实现困难的电路板布局,达到苛刻的电磁兼容要求,也具有更好的散热特性。其缺点在于使用的元件较多,成本高,会增加电路板占用面积,而这会给电路板空间弥足珍贵的手机等便携设备设计带来更大挑战。这种方案正在逐步淘汰之中。

对于集成式充电方案而言,它集成了大量的功能,所需的外围器件非常少,易于实现小尺寸的外形因数,利于降低电路板布局的复杂性。包括安森美半导体在内的众多厂商都支持这种方案。不过,由于工艺和功耗方面的原因,集成式充电解决方案对充电电流的大小 会有严格限制。此外,集成式方案布局比较麻烦,缺乏灵活性,难以满足产品功能差异化要求,所集成的众多功能对有些客户来说可能意味着过多的限制。因此,这种方案主要适合于对灵活性要求不高的高产量应用。

图2 “PMU+充电功率元件”型充电解决方案的结构示意图

相比较前两种方案而言,“PMU/PMIC+充电功率元件”这种方案处于主流地位。这种方案综合了集成度与灵活性的优势,适用于必须支持不同市场的产品。基于这种理念的设计不会占用太多电路板空间,但元件的位置可以更灵活,且易于实现产品的差异化。在这种方案中,外部充电功率元件可以是场效应管(FET)、双FET、双极型晶体管(BJT)和FETKY(MOSFET和肖特基二极管共同封装在一起)等。这种解决方案的结构示意图如图2所示。

如上所述,在第三种解决方案中,可以选用不同的外部充电功率元件。那么,究竟什么样的充电功率元件更合适呢?我们可以通过最坏情况来予以分析。

假定充电器(电源适配器)提供的最低电压是4.75 V,而电池电压为4.3 V,充电器电流为500 mA,而感测电阻为200 mΩ,PCB电阻为100 mΩ。这样对手机充电电路而言,就在电源输入和电池之间留出了0.45 V的电压裕量。

图3 FETKY和双FET方案的结构示意图

结合图2和图3(a)所示,充电由PMU控制,MOSFET充当充电电流的传输元件。这里计算一下通过这个充电电路中的两个传输元件(MOSFET和肖特基二极管)的压降。

Vdropout = 充电电流×Rds(on)+Vf = 0.5 A×Rds(on)+Vf

在最坏情况下,充电器电流为500 mA时,压降(Vdropout)概算为300 mV。也就是当充电器电流为500 mA时,典型的肖特基二极管的正向电压(Vf)已经是400 mV,这就导致无法提供足够的电压裕量。而且随着充电电流的增加,肖特基二极管所促成的0.4 V极高压降更会使其成为一个阻塞点。因此,在今后的解决方案中应该避免使用FETKY解决方案。

而在另一方面,通过用具有低V CE(Sat)的晶体管或者具有低Rds(on)的MOSFET代替肖特基二极管,可以降低传输元件上的压降,从而符合所需要的有限电压裕量要求。例如,双FET用作充电功率元件(如图3(b)所示)就是一个更加合适的选择。在这方面,安森美半导体的NTLJD3115P和NTHD4102P就是非常适合的选择。其中,NTLJD3115P是一款-20 V、-4.1 A、μCool? 双P沟道功率MOSFET,它采用2×2 mm的WDFN封装,具有极低的导通阻抗,其0.8 mm的高度也使其非常适合纤薄的应用环境;它针对便携设备中的电池和负载管理应用进行了优化,适合于锂离子电池充电和保护电路应用及高端负载开关应用。而NTHD4102P是一款-20 V、-4.1 A双P沟道ChipFETTM功率MOSFET,同样具有较小的占位面积和极低的导通阻抗,适合于纤薄的便携应用环境。

具体而言,采用双FET的有利因素包括:阻塞反向电流、允许反向给蓝牙配件充电,以及导通阻抗(Rds(on))较低。此

- 利用palm点金石进行手机无线充电改装(12-09)

- 一种新颖的双G型超宽频手机内置天线仿真优化(12-09)

- 很棒的创意——一勺水可产生10小时手机电量的充电器(12-08)

- 移动电源充电 到底能不能把手机充坏?(12-08)

- 智能手机一小时充好电管理方案之经验分享(12-08)

- 魅族MX4/小米4等手机锂电池续航谁最牛?(12-07)