零电压反激式开关电源芯片IRIS4015原理及设计要点

时间:03-15

来源:互联网

点击:

1. 引言

目前单片开关稳压电源有多种多样,如TOP-switch、Tiny-switch、Cool-set等,这些单片开关稳压电源均工作在硬开关状态,开关损耗和EMI较大。为克服硬开关的缺点可用软开关工作方式。在反激式开关电源中以无损耗缓冲电路和准谐振工作方式最为简单,而且准谐振工作方式可以实现零电压的开通和关断,在各种准谐振的解决方案中IRIS4015是一种很好的方案。

2. IS4015工作原理分析

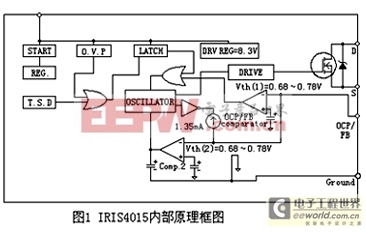

IRIS4015是单片准谐振式反激式开关电源中MOSFET和控制IC的集成,如图1,有五个功能引脚:源极(S)、漏极(D)、控制IC的接地端(GND)、电源(Vcc)、过电流和电压反馈输入端(OCP/FB)。

IRIS4015可以工作在准谐振模式下,该模式下频率可变,在轻载和高电源电压下达最大。IRIS4015具有各种保护电路如:温度补偿的逐个脉冲过电流保护(OCP)、过电压锁定保护(OVP)、热关闭电路(TSD);启动电流最大不超过100uA,有源低通滤波器可使轻载时稳定度提高;内置温度补偿基准电压;具有可调门驱动;并且可以通过外部元件调整开关速度用于EMI控制。

2.1 IRIS4015工作原理

IRIS4015的启动工作方式UC3842相似,不再赘述。注意:启动电阻Rs和启动电容C2的取值范围如下:

C2:22μF — 100μF

Rs:47KΩ — 68KΩ (输入电压110伏),82KΩ — 150KΩ (输入电压220伏)

反馈和控制电路工作,振荡器和限流控制方式。

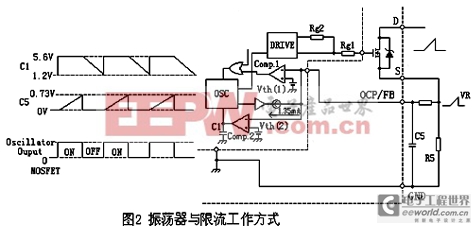

振荡器利用IC中C2的充放电产生脉冲信号确定MOSFET的关断时间,如图2,这是IC在没有电压控制反馈时,振荡器的工作过程。当MOSFET导通时,内置C1被充电到约5.6V,漏极电流ID流过R5产生压降VR5(其波形为ID的锯齿波),VR5被反馈到OCP/FB端来控制初级电流(初级电感电流控制方式),当OCP/FB端电压达到门限电压Vth(1)(0.73V)时,比较器1改变状态,振荡器输出关断信号,MOSFET关断。

当MOSFET关断时C1开始被缓慢放电,C1电压下降,其下降过程由C1值和放电电流确定,当C1的值降到1.2V左右时,振荡器输出导通信号,MOSFET重新导通,同时C1瞬间充电到5.6V左右,电路重复以上振荡周期。上述由VR5(ID)的斜率确定的时间就是MOSFET的导通时间,C1和直流放电电路所确定的固定时间是MOSFET的关断时间,这个固定时间被直流放电电路限制在50μS左右。

2.2 次级电压控制方式

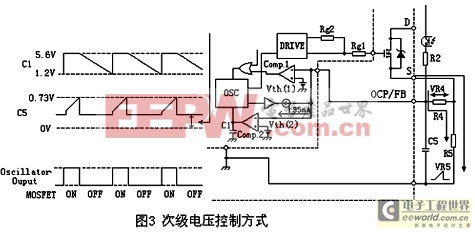

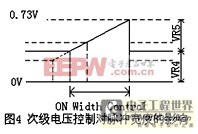

次级输出为电压控制方式,如图3所示,在输出端设计的过电压使光电耦合器的LED中有电流流过,引起反馈电流流过光电耦合器的三极管,并依次流过R4和R5,产生压降VR4和VR5,使COMP1反向所需的VR5电压(ID的峰值)被VR4(由FB电流产生)控制。因此如图4所示:VR4在OCP/FB端产生附加直流偏置电压,通过这一附加偏置电压缩短OCP/FB端电压达到门限电压V th(1)的0.73V所需的时间来降低MOSFET的导通时间。这将导致反向变压器的储能降压,通常,来自VR4的偏压在轻载时增加,而且MOSFET导通时冲击电流产生的噪声能使比较器1误动作,为避免这个问题,可在MOSFET截止时,用一个无源低通滤波器R4、C5和有源滤波器来减小OCP/FB与GND之间的动态静态阻抗,有源低通滤波器是OCP/FB端与地之间的一个1.35mA直流旁路,它将使MOSFET导通时OCP/FB端的静态阻抗降低一半左右,而MOSFET导通时产生噪声由C5来吸收

2.3 准谐振工作方式的分析

准谐振方式是在VDS最小情况下的情况下,由初级线圈电感和一个缓冲电容器提供一个控制MOSFET开通 的谐振信号,以降低开关损耗。在这种工作模式下的OCP/FB将高于Vth(2)=1.45V(最大6V),当这个电压维持在Vth(1)以上时,MOSFET保持关断状态(注意:准谐振信号最小持续时间1us)。因此,准谐振模式下的谐振频率的一半周期用来使MOSFET导通。

漏极和源极之间的谐振电容C3与变压器初级电感形成谐振电路,在控制绕组D与OCP/FB端加一个由C3、D4、R5组成的延迟电路产生准谐振信号,在MOSFET截止时控制比较器2并触发准谐振方式。由 于延迟电路的存在,即使变压器上的全部能量都传送到次级线圈,反馈到OCP/FB的准谐振信号也不会立即下降,这是因为C4和C5由有源滤波器(1.35mA的电流吸收器)和R6、R7的复合阻抗放电,某周期后,电压降到Vth(1)或低于它,延迟时间取决于初级电感和C3。调整C4使得当MOSFET和VDS达到准谐振信号的最低点时,MOSFET导通,因此延迟时间由C4和C5的放电时间确定,即使没有C4,也会有一段延迟时间,当OCP/FB端和GND之间的最大电压为6V时,准谐振信号必须低于这个电压。

3. 电路设计要点

应用电路如图5,其主要选择和计算的元件有:变压器、R3、R4、R5和谐振电容器。

目前单片开关稳压电源有多种多样,如TOP-switch、Tiny-switch、Cool-set等,这些单片开关稳压电源均工作在硬开关状态,开关损耗和EMI较大。为克服硬开关的缺点可用软开关工作方式。在反激式开关电源中以无损耗缓冲电路和准谐振工作方式最为简单,而且准谐振工作方式可以实现零电压的开通和关断,在各种准谐振的解决方案中IRIS4015是一种很好的方案。

2. IS4015工作原理分析

IRIS4015是单片准谐振式反激式开关电源中MOSFET和控制IC的集成,如图1,有五个功能引脚:源极(S)、漏极(D)、控制IC的接地端(GND)、电源(Vcc)、过电流和电压反馈输入端(OCP/FB)。

IRIS4015可以工作在准谐振模式下,该模式下频率可变,在轻载和高电源电压下达最大。IRIS4015具有各种保护电路如:温度补偿的逐个脉冲过电流保护(OCP)、过电压锁定保护(OVP)、热关闭电路(TSD);启动电流最大不超过100uA,有源低通滤波器可使轻载时稳定度提高;内置温度补偿基准电压;具有可调门驱动;并且可以通过外部元件调整开关速度用于EMI控制。

2.1 IRIS4015工作原理

IRIS4015的启动工作方式UC3842相似,不再赘述。注意:启动电阻Rs和启动电容C2的取值范围如下:

C2:22μF — 100μF

Rs:47KΩ — 68KΩ (输入电压110伏),82KΩ — 150KΩ (输入电压220伏)

反馈和控制电路工作,振荡器和限流控制方式。

振荡器利用IC中C2的充放电产生脉冲信号确定MOSFET的关断时间,如图2,这是IC在没有电压控制反馈时,振荡器的工作过程。当MOSFET导通时,内置C1被充电到约5.6V,漏极电流ID流过R5产生压降VR5(其波形为ID的锯齿波),VR5被反馈到OCP/FB端来控制初级电流(初级电感电流控制方式),当OCP/FB端电压达到门限电压Vth(1)(0.73V)时,比较器1改变状态,振荡器输出关断信号,MOSFET关断。

当MOSFET关断时C1开始被缓慢放电,C1电压下降,其下降过程由C1值和放电电流确定,当C1的值降到1.2V左右时,振荡器输出导通信号,MOSFET重新导通,同时C1瞬间充电到5.6V左右,电路重复以上振荡周期。上述由VR5(ID)的斜率确定的时间就是MOSFET的导通时间,C1和直流放电电路所确定的固定时间是MOSFET的关断时间,这个固定时间被直流放电电路限制在50μS左右。

2.2 次级电压控制方式

次级输出为电压控制方式,如图3所示,在输出端设计的过电压使光电耦合器的LED中有电流流过,引起反馈电流流过光电耦合器的三极管,并依次流过R4和R5,产生压降VR4和VR5,使COMP1反向所需的VR5电压(ID的峰值)被VR4(由FB电流产生)控制。因此如图4所示:VR4在OCP/FB端产生附加直流偏置电压,通过这一附加偏置电压缩短OCP/FB端电压达到门限电压V th(1)的0.73V所需的时间来降低MOSFET的导通时间。这将导致反向变压器的储能降压,通常,来自VR4的偏压在轻载时增加,而且MOSFET导通时冲击电流产生的噪声能使比较器1误动作,为避免这个问题,可在MOSFET截止时,用一个无源低通滤波器R4、C5和有源滤波器来减小OCP/FB与GND之间的动态静态阻抗,有源低通滤波器是OCP/FB端与地之间的一个1.35mA直流旁路,它将使MOSFET导通时OCP/FB端的静态阻抗降低一半左右,而MOSFET导通时产生噪声由C5来吸收

2.3 准谐振工作方式的分析

准谐振方式是在VDS最小情况下的情况下,由初级线圈电感和一个缓冲电容器提供一个控制MOSFET开通 的谐振信号,以降低开关损耗。在这种工作模式下的OCP/FB将高于Vth(2)=1.45V(最大6V),当这个电压维持在Vth(1)以上时,MOSFET保持关断状态(注意:准谐振信号最小持续时间1us)。因此,准谐振模式下的谐振频率的一半周期用来使MOSFET导通。

漏极和源极之间的谐振电容C3与变压器初级电感形成谐振电路,在控制绕组D与OCP/FB端加一个由C3、D4、R5组成的延迟电路产生准谐振信号,在MOSFET截止时控制比较器2并触发准谐振方式。由 于延迟电路的存在,即使变压器上的全部能量都传送到次级线圈,反馈到OCP/FB的准谐振信号也不会立即下降,这是因为C4和C5由有源滤波器(1.35mA的电流吸收器)和R6、R7的复合阻抗放电,某周期后,电压降到Vth(1)或低于它,延迟时间取决于初级电感和C3。调整C4使得当MOSFET和VDS达到准谐振信号的最低点时,MOSFET导通,因此延迟时间由C4和C5的放电时间确定,即使没有C4,也会有一段延迟时间,当OCP/FB端和GND之间的最大电压为6V时,准谐振信号必须低于这个电压。

3. 电路设计要点

应用电路如图5,其主要选择和计算的元件有:变压器、R3、R4、R5和谐振电容器。

- 高端准谐振零压开关反激式转换器中的ESBT技术(12-09)

- 总结反激式电源常见噪声源及解决方案(12-09)

- 基于UCC28600准谐振反激式开关电源的方案(12-08)

- 基于LTMR4644的稳压电源解决(12-08)

- 反激隔离电源设计解决MCU的供电问题(12-08)

- 一款IC开关电源的反激式变压器设计方案(一)(12-08)