时域时钟抖动分析(一)

相位噪声整合抖动结果都极为不同,而“表 1”的 SNR 测量情况也反映这种现象。

图 7 近区相位噪声决定主容器附近 FFT 容器的振幅

设置正确的整合上限

图 6 所示相位噪声图抖动贡献量为 ~360 fs,其频率偏移为 10 到 100MHz 之间。这比 100Hz 到 10MHz 之间偏移的所有 ~194 fs 抖动贡献值要大得多。因此,所选整合上限可极大地影响计算得到的时钟抖动,以及预计SNR匹配实际测量的好坏程度。

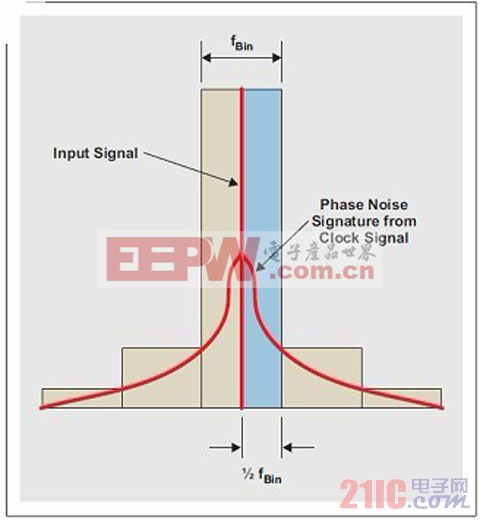

要确定正确的限制,您必须记住采样过程中非常重要的事情是:来自其他尼奎斯特区域的时钟信号伪带内噪声和杂散,正如其出现在输入信号时表现的那样。因此,如果时钟输入的相位噪声不受频带限制,同时没有高频规律性衰减,则整合上限由变压器(如果使用的话)带宽和 ADC 自身的时钟输入设定。一些情况下,时钟输入带宽可以非常大;例如,ADS54RF63 具有 ~2 GHz 的时钟输入带宽,旨在允许高时钟转换速率的高阶谐波。

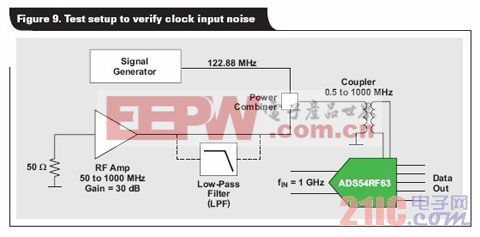

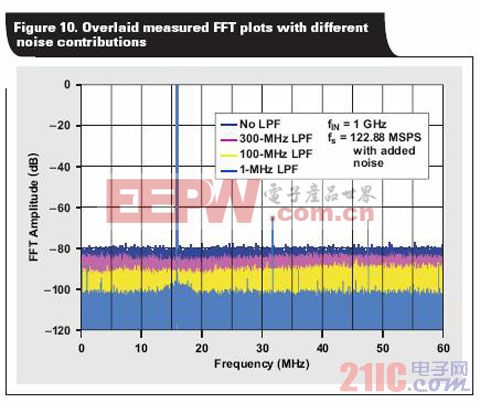

若想要验证时钟相位噪声是否需要整合至时钟输入带宽,则需建立另一个实验。ADS54RF63 再次工作在 122.88 MSPS,其输入信号为 1GHz,以确保 SNR 抖动得到控制。我们利用一个 RF 放大器,生成 50MHz 到 1GHz 的宽带白噪声,并将其添加至采样时钟,如图 9 所示。之后,我们使用几个不同低通滤波器 (LPF) 来限制添加至时钟信号的噪声量。

ADS54RF63 的时钟输入带宽为 ~2 GHz,但由于 RF 放大器和变压器都具有 ~1 GHz 的 3-dB带宽,因此有效 3-dB 时钟输入带宽被降低至 ~500 MHz。“表

该实验表明,时钟相位噪声必需非常低或者带宽有限,较为理想的情况是通过一个很窄的带通滤波器。否则,由系统时钟带宽设定的整合上限会极大降低 ADC 的 SNR。

结论

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。“第 2 部分”将会介绍如何使用这种估算方法来推导 ADC 的 SNR,以及所得结果与实际测量结果的对比情况。

仔细观察某个采样点,可以看到计时不准(时钟抖动或时钟相位噪声)是如何形成振幅变化的。由于高 Nyquist 区域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采样带来输入频率的增加,固定数量的时钟抖动自理想采样点产生更大数量的振幅偏差(噪声)。另外,图 2 表明时钟信号自身转换速率对采样时间的变化产生了影响。转换速率决定了时钟信号通过零交叉点的快慢。换句话说,转换速率直接影响 ADC 中时钟电路的触发阈值。

图 2 时钟抖动形成更多快速输入信号振幅误差

时钟抖动导致的 SNR 减弱 有几个因素会限制 ADC 的 SNR,例如:量化噪声(管线式转换器中一般不明显)、热噪声(其在低输入频率下限制 SNR),以及时钟抖动(SNRJitter)(请参见下面方程式 1)。SNRJitter 部分受到输入频率 fIN(取决于 Nyquist 区域)的限制,同时受总时钟抖动量 tJitter 的限制,其计算方法如下:

- 具扩展频谱频率调制的低EMI DC/DC稳压器电路(12-24)

- EMI/EMC设计讲座(三)传导式EMI的测量技术(07-20)

- 扩展射频频谱分析仪可用范围的高阻抗FET探头(07-14)

- 开关电源基于补偿原理的无源共模干扰抑制技术(08-27)

- 开关电源的无源共模干扰抑制技术(11-12)

- 省电设计使DDS更适合便携应用(12-19)