一种改进的无桥Boost功率因数校正电路

摘要:无桥电路由于电流流经功率回路中半导体器件的减少,相对传统整流桥的电路拓扑效率得到提升,在低压输入和中大功率应用场合意义显著。现有的无桥电路存在EMI问题突出等不足,为此对现有无桥Boost型电路进行改进,提出了具有高效率、高功率因数和低EMI噪声的新型无桥Boost功率因数校正(PFC)拓扑,在理论分析的基础上使用Pspice 9.2进行仿真验证。设计了一台85~265 V交流输入,400 V/300 W输出的实验样机,进一步验证了该无桥变换器的良好电气特性。

关键词:功率因数校正;无桥变换器;电磁干扰

1 引言

无桥PFC变换器在低压输入和中大功率场合具有明显的效率优势,但现有无桥PFC变换器仍不成熟,文献对现有的多种无桥电路进行比

较,指出双Boost无桥拓扑具有电流检测电路简单、导通损耗低、EMI噪声小且两个开关管可以共用同一PWM驱动信号等特点,成为现有无桥Boost型拓扑工程应用的最优选择。但此电路的缺点是开关管只能选择无反并二极管封装的IGBT,因此电路的工作频率将受到限制,在功率不大的情况下,难以选择合适的控制策略,如临界电流模式(BCM)控制。若开关管选用功率MOSFET,其中一个电感正常工作时,另一电感中会有逆向电流产生,此电流对电路的动态性能和效率都会产生不良影响,并且此电流的存在还可能导致连接于交流输入端和输出地之间慢速二极管的关断,增大共模噪声。另外,若不希望影响电路的功率因数且精确采样开关管电流,则两开关管不适合共用一个电流采样电阻,独立采样势必增加采样电路的复杂性。在此针对现有的双Boost拓扑电路存在的问题进行改进,提出了无需使用IGBT便能抑制电感逆向电流的新型无桥Boost PFC电路,并采用BCM进行了仿真和实验验证。

2 新型拓扑原理分析

2.1 主电路拓扑结构

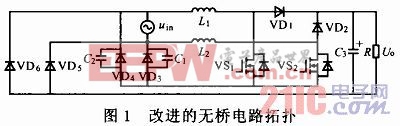

图1示出所提出的新型无桥Boost PFC电路拓扑,其中VD1~VD4为快管,VD5,VD6为慢管,C1,C2为高频电容。

当交流电源uin处于正半周(即上正下负)时,uin,VS1,VD3构成L1的充电回路,uin,VD1,VD5,输出滤波电容C3及负载R构成L1的放电回路;当uin处于负半周时,uin,VS2,VD4构成L2的充电回路,uin,VD2,VD6,C3及R构成L2的放电回路。

2.2 电路工作阶段分析

由于BCM下的Boost变换器中快恢复二极管自然关断,避开了反向恢复问题,变换器中的开关管为零电流开通,并且功率MOSFET开通前的准谐振过程将有效减小其自身的容性开通损耗。以BCM控制为例,分析所提出的改进拓扑,其中VS1,VS2共用电流采样电阻和驱动信号。电路工作的关键参量波形如图2所示。

改进变换器的工作过程如下:

阶段1 [t1~t2] uin处于正半周期,VS1开通,uin经VS1,VD3对L1进行充电,C3对R进行放电,同时流过VS1的部分电流经VS2反向流过L2。

阶段2 [t2~t3] 在t2时刻,VS1关断,L1与uin一同经VD1,VD5对C3及R供电,此时VD3阻断,L2与C1,C2经VS2的体二极管进行谐振。L2上的能量以谐振的方式传递给C1,C2,L2上的电流iL2减小,VD3,VD4电压升高,在t3时刻,iL2下降至零,即IL2得到“复位”。

阶段3 [t3~t4] 由于VS2的体二极管反向不通,iL2保持为零,L1同uin一起持续向输出供电,在t4时刻,L1上的电流iL1下降至零。

阶段4 [t6~t7] uin处于负半周期,VS2开通,uin经VS2,VD4对L2进行充电,C3对R进行供电,与阶段1类似,此时L1产生逆向电流。

阶段5 [t7~t8] 在t7时刻,VS2关断,L2与uin一同经过VD2,VD6对C3以及R供电。此时,VD4阻断,L1与C1,C2经VS1的体二极管进行谐振,L1上的能量以谐振方式传递给C1,C2,iL1减小,VD3,VD4的电压升高,在t8时刻,iL1下降至零,即iL1得到“复位”。

阶段6 [t8~t9] 由于VS1的体二极管反向不通,iL1保持为零,L2同Uin一起持续向输出供电,在t9时刻,iL2下降至零。

电路稳态工作时以[t0~t10]为周期持续工作。在[t0~t5]期间,uin处于正半周期,阶段1,阶段2和阶段3交替进行,周而复始;在[t5~t10]期间,uin处于负半周期,阶段4,阶段5和阶段6交替进行,周而复始。由以上分析及图2波形可知,变换器输入端对输出地的电位差(即VD5,VD6所承受的电压)基本上为平滑的工频正弦半波,而变换器输入端对芯片地的电位差(即VD3,VD4所承受的电压)的正弦半波中仅包含很低幅值的电位跳变,因此而引发的共模噪声小。

3 改进拓扑仿真分析

用Pspice 9.2仿真软件对所提出的改进无桥电路拓扑(输入端接入差模滤波器)进行仿真,L1,L2的电流仿真波形如图3所示。可见,电感中的逆向电流已得到有效抑制。由于差模电容承受高频电流而引起的高频电压波动经过C1,C2进行分压,导致VD3,VD4的电压波形与图2中VD3,VD4的波形略有区别,VD3电压仿真波形如图4所示。

- 基于软开关技术的能量恢复电路及其检测(12-09)

- 如何选择功率因数校正(PFC)拓扑?(12-30)

- 双重单级PFC软开关变换器(08-23)

- 开关电源功率因素校正(PFC)及其工作原理(02-25)

- 一种有源功率因数校正电路及控制方法的设计(11-22)

- 三相功率因数校正系统的设计考虑(11-11)