解析基于开关电源驱动的高速ADC设计方案

时间:05-24

来源:互联网

点击:

低。

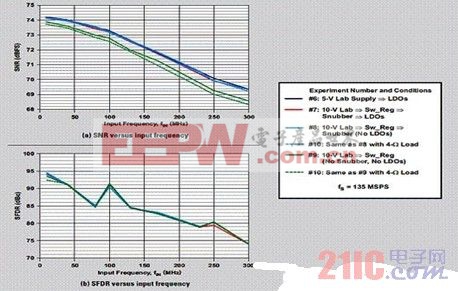

图12:10到300MHz的输入频率扫描。

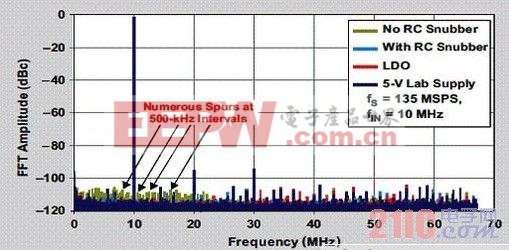

比较图13所示FFT图,我们知道无RC缓n器SNR稍微减少的塬因。去除RC缓n器电路后,在ADS6148输出能谱中,我们可看到分鸭涓粼嘉500kHz(TPS5420开关频率)的众多小突波,如图13所示。相较于ADS5483,这些小突波更具主导性,并且因为ADS6148的固有低PSRR SNR大幅降低。但是,图13所示FFT图还显示添加的RC缓n器电路较好地弥补了这一不足。

图13:大批突波的65k点FFT图。

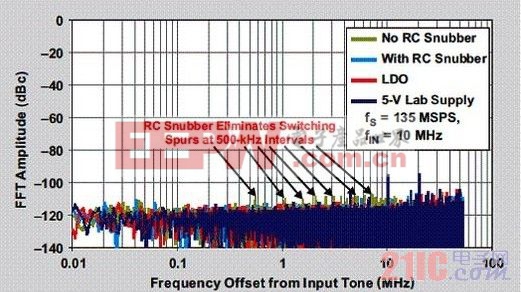

图14所示标驶FFT图显示交换式稳压器的突波高出ADC平均杂讯层约5到6dB。其非常低,以至于其对SFDR减少无法产生影响,但却明显地影响了ADC的SNR。

图14:标驶FFT图显示使用RC缓n器的好处。

ADC 设计 方案 高速 驱动 基于 开关电源 解析 相关文章:

- S3C2440A嵌入式手持终端电源管理系统设计(01-11)

- 基于CAN通信的电源监控系统的设计(04-06)

- 基于MSP430单片机的电源监控管理系统(04-20)

- 适用于全球交流电源的单节锂离子电池充电器设计(06-07)

- GPIB芯片TNT4882在多路程控电源中的应用(06-08)

- AD7656的原理及在继电保护产品中的应用(06-18)