THS4271集成电路实验特性及其应用

摘要:以TI公司生产的集成运放THS4271为基础搭建实验测试电路,在定义的条件下实验,分别测量了运放的输入失调电压UIO,输入失调电流IIO,共模抑制比CMRR,开环差模放大倍数AUd等主要参数。同时对测量的数据对应的相应的参数进行了简单分析。基于THS4271的单位增益稳定,低失真,高压摆率等特性,举出几个应用实例,来说明其在某些工程领域有一定的应用价值,供今后的使用者参考。

关键词:THS4271;集成运放;实验;应用

虽然经过多年的发展,在现代集成电路与系统芯片(Systemon Chip,SoC)中,集成电路运算放大器的应用依然非常广泛,并往往由应用需要对其性能提出苛刻的要求。因此围绕高性能集成电路运算放大器的研究经久不衰。文中结合实际项目的需要,对THS4271集成运放的主要参数进行了测试,并对结果和其应用进行了讨论,利于今后实验的开展,同时为器件的使用者提供参考。

1 芯片介绍

THS4271是TI公司生产的低噪声,高压摆率,单位增益稳定电压反馈放大器,其设计正常工作电压范围是5~15 V。兼有低噪声,高压摆率,宽带宽,低失真以及单位增益稳定的特性,使得THS4271具有高性能的表现。此放大器的使用者可以在一个较宽的频带上获得实验所需的较高的动态范围,而不必为放大器在失偿期间的稳定性担忧。该系列的放大器的封装形式有SOIC,带有PowerPAD的MSOP,以及带PowerPAD无引线的MSOP。THS4271典型特征参数如表1所示。

THS4271原件形状,引脚分布及各引脚功能如图1所示。(其中NC代表悬空)

2 实验原理

2.1 输入失调电压

理想运算放大器(简称运放)的输入信号为零时,其输出直流信号也应该为零。但实际上如果没有外界的调零措施,由于运放内部参数不完全对称,输出电压往往不为零。这种输入为零时输出不为零的现象称为集成运放的失调。

在室温和标准电源电压下,为了使输出端的直流电压为零,必须先在输入端加一个直流电压作为补偿电压,以抵消偏离零点的输出电压,而这个加在输入端的电压即被称为输入失调电压UIO。显然,UIO数值越小,说明运放的参数对称性越好。

2.2 输入失调电流

运放的偏置电流是指运放输入级差分对管的基极电流IB1和IB2,由于晶体管参数的分散性,IB1≠IB2。当输入信号为零时,运放的两个输入端的基极偏置电流之差称为输入失调电流,IIO,即IIO=|IB1-IB2|。显然,IIO的存在将使输出端零点偏移,信号源阻抗越高,失调电流影响越严重。

2.3 共模抑制比

共模抑制比是用来表征运放对共模信号抑制能力大小的参数。定义为运放的差模电压放大倍数Ad与共模电压放大倍数Ac之比:CMRR=Ad /Ac;用分贝表示:CMRR=20lg(Ad/Ac)dB。共模抑制比在应用中是一个很重要的参数,理想运放对输入的共模信号输出为零,但在实际的集成运放中,其输出不可能没有共模信号的成分,输出端共模信号越小,说明电路对称性越好,运放对共模干扰信号的抑制能力越强,即CMRR越大。

2.4 开环差模放大倍数

集成运放在没有外部反馈时的直流差模放大倍数称为开环差模电压放大倍数,用Aud表示。定义为开环输出电压幅值UO与两个差分输入端之间所加信号电压幅值Uid之比:AUd=UO/Uid。

3 测试电路,数据及分析

3.1 输入失调电压测量

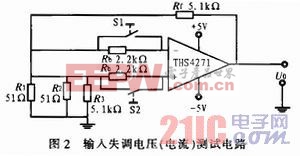

失调电压测试电路原理图如图2所示。闭合开关S1及S2(实验时用导线代替),使电阻Ra短接,测量此时的输出电压UO即为输出失调电压,换算到输入端,可得输入失调电压UIO=R1·UO/(R1+Rf),经实验测量UO=385 mV,带入上式可得UIO=3.85mV。

3.2 输入失调电流测量

输入失调电流IIO的大小反映了运放内部差动输入级两个晶体管β的适配度,由于IB1和IB2本身的数值很小(大约在微安级别),因此他们的差值通常不是直接测量的,测试电路原理如图2所示。

IIO的测量分两步:

1)闭合开关S1和S2,在低输入电阻下,测出输出电压为UO1,其中UO1=(R1+Rf)·UIO/R1,如前所述,这就是由输入失调电压UIO引起的输出电压。

2)断开S1和S2,两个输入电阻RB接入电路,测得此时的输出电压为UO2。由于RB阻值较大,流经它们的输入电流IB1、IB2的差异将变成输入电压的差异,即IIO·RB=|IB1-IB2|·RB,考虑同时存在的输入失调电压的影响,可得UO2=(UIO+IIO·RB)·(R1+RF)/R2。

综上所述,将两次测得的数据UO1=0.392 V和UO2=0.693 V代入IIO=(UO2-UO1)·R1/RB(R1+Rf),即可得到电路的输入失调电流IIO=11 1.16 nA。

3.3 共模抑制比测量

共模抑制比测量电路如图3所示。集成运放在闭环状态下的差模电压放大倍数为Ad=Rf/R1,当接入共模输入信号幅值为UiC时,测得输出幅值为UOC,则共模电压放大倍数为Ac=UOC/UIC,得到共模抑制比CMRR=Ad/AC=Rf·UIC/(R1·UOC)。实验测得,Ac=2.4,则CMRR=32.4 dB。

及其 应用 特性 实验 集成电路 THS4271 相关文章:

- 一种全桥同步整流器的设计及其应用(10-23)

- 压力传感器的激励电源及其作用研究分析(09-18)

- 电力系统中的谐波问题及其解决方法(07-28)

- RCC变压器设计及其与反激电路的对比(07-28)

- 三相SPWM简介及其在变频器中的实现方法(07-17)

- 三相SPWM简介及其优化方法(07-17)