应用于数字阵列的多通道波形产生系统设计

摘要:直接数字频率合成(DDS)是数字阵列雷达(DAR)实现收发数字波束形成的关键技术之一。给出了一种基于DDS技术的多通道波形产生系统的设计方案,该方案在25 cm×12 cm的PCB板上实现了波形产生、波形捷变与幅相控制的系统集成设计。该系统能同时产生16路频率、幅度和相位独立控制的中频雷达信号,满足数字阵列雷达对收发阵列单元的高集成度、小型化、低成本和多功能的要求;系统实现的主要技术指标为;信号带宽1~1 20 MHz可变,通道隔离度大于60 dBc,窄带脉内信噪比大于65 dBc,满足数字阵列雷达技术指标的要求。

关键词:数字阵列雷达;波形产生;直接数字频率合成;小型化

0 引言

数字阵列雷达(Digital Array Radar,DAR)在接收和发射模式下均采用数字波束形成(Digital Beam Forming,DBF),实现射频信号功率在空域灵活分配与接收,获得优良的收发波束特性,从而提升了雷达系统的多项性能,是雷达重要发展趋势之一。在数字阵列雷达中,直接数字频率合成(Direct Digital Synthesizer,DDS)是实现雷达波形产生与发射波束控制的最常用的方案之一。基于DDS技术的多通道波形产生系统不仅可以方便地产生各种雷达波形,还可以在数字域灵活地对阵列天线进行相位和幅度加权,实现发射波束的快速、高精度控制,从而实现雷达波形产生、波形捷变与幅相控制的一体化设计。

1995年,Adrian Garrod提出了数字T/R组件的基本概念,研制了13单元收发全DBF相控阵雷达实验系统,该系统采用DDS技术实现了波形产生系统,其信号样式为线性调频,瞬时带宽小于1 MHz;林肯实验室于2003年完成了一个S波段宽带数字阵列试验系统,该系统采用DDS技术产生线性调频信号,拥有宽带(500 MHz)和窄带(10 MHz)两种工作方式;文献也介绍了多种采用DDS技术实现波形产生与发射DBF控制的数字阵列系统。上述文献介绍的大都是应用于DAR实验验证系统中的波形产生系统,其系统结构较为复杂,系统集成度较低,成本较高;而数字阵列雷达发展尤其是大规模数字阵列的兴起,对阵列单元的集成度、体积、成本和功能多样化等方面提出了进一步的要求。本文介绍了一种基于DDS技术的多通道、小型化、低成本的波形产生系统的设计,该系统在25 cm×12 cm的PCB板上实现了16通道波形产生、波形捷变与幅相控制的一体化设计,能同时产生16路频率、幅度和相位独立控制的中频雷达信号,信号带宽1~120 MHz可变,通道隔离度大于60 dBc,该系统已成功应用于某数字阵列雷达。

1 数字波形产生原理与幅相控制方法

应用于雷达波形产生的DDS技术主要分为基于存储器的直接数字波形合成(Direct Digital WaveformSynthesizer,DDWS)和基于累加器的直接数字频率合成(Direct Digital Frequency Synthesizer,DDFS)两类。DDWS技术是根据高速采样时钟,直接读取预先存储在高速存储器中的数字波形,进行数/模转换获得所需模拟波形,其特点是简单灵活,只要存储器时钟足够高,叮以获得超宽带LFM信号,不足之处在于需要大容量存储器,系统结构较为复杂。DDFS技术是通过相位累加器得到当前相位值,然后利用该值寻址ROM查找表,读出相应的信号幅值,最后经数/模变换获得模拟波形,其特点是频率分辨率高、波形参数控制灵活,不足之处在于限于DDS器件的水平其时钟频率不够高,难以产生超宽带波形。

对于大规模数字阵列,高集成度、小型化、低成本是系统设计的关键问题之一。随着数字集成电路的发展,DDFS芯片集成度和时钟频率进一步提高,尤其是单芯片多通道DDFS芯片的出现,给实现高集成度、小型化、低成本的阵列雷达多通道波形产生系统提供了便利。针对实际数字阵列系统指标要求产生中心频率为140 MHz,带宽为1~120 MHz的线性调频,设计中采用DDFS技术实现多通道波形产生是最优的方案。

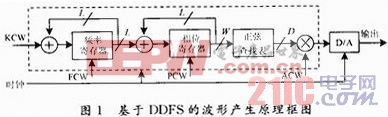

图1给出了一种适用于数字阵列雷达基于DDFS技术的雷达波形产生系统原理框图,DDS核中的相位累加器完成调相功能,而频率累加器和相位累加器两级串联结构完成调频功能,正弦查找表后的乘法器则完成对波形信号幅度的控制,于是实现了阵列雷达的波形产生、波形捷变和幅相控制的一体化设计。

2.1 多通道波形产生系统结构与硬件设计

根据上文的分析,采用DDFS技术来实现该多通道波形产生系统,考虑到系统指标实现和成本要求,选用ADI公司的四通道高集成度DDS芯片AD9959作为系统的核心芯片,该芯片最高时钟频率达到500 MHz,包含了四路频率、相位和幅度独立可控的DDS核,DDS核的内部结构与图1所示的原理框图一致。设计中采用了4片AD9959芯片,配以外围逻辑电路、转换电路,在单块PCB板上实现了16通道独立可控的中频雷达信号的系统集成设计,系统结构框图如图2所示。AD9959时钟频率选为480 MHz,FPGA的同步时钟为60 MHz;采用三片FPGA组成逻辑控制电路,完成对AD9959的初始化配置,对波形控制系统送来的控制码进行译码,并行计算十六路DDS通道波形的频率、幅度、相位等控制参数,转化为DDS寄存器控制码,完成对16个通道相应寄存器的读写操作。这样,利用AD9959的频率和幅相控制功能,在完成数字波形信号产生的同时,对数字阵列的每个发射单元波形的频率、相位和幅度进行独立控制,该数字信号经D/A变换成模拟中频信号,然后由线性上变频通道完成发射频率扩展形成射频信号,最后射频信号经天线辐射单元实现发射DBF。

- 开关电源纹波产生以及抑制的方法(09-14)

- 旋转磁场的产生演示器(08-28)

- 高频变压器中传导EMI产生机理(05-29)

- 推挽逆变器中两开关管漏极产生尖峰的原因及改进方法(05-10)

- 电源纹波的产生、测量和抑制(03-29)

- 怎样采用一个 µModule 降压型稳压器从正输入产生负输出电压(01-09)