用于实时时钟的32.768kHz晶振电路分析与设计

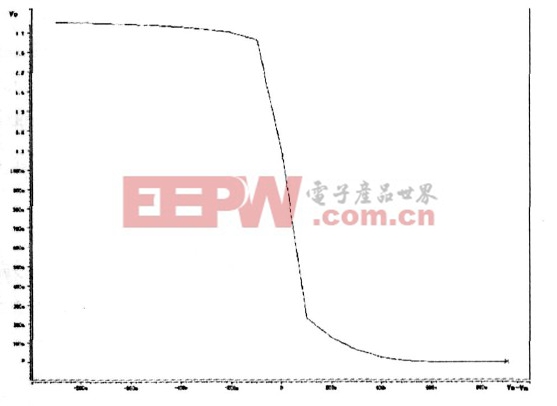

示电路搭建仿真模型用Hspice 进行仿真。图2 中需要给电路提供一个直流电平,所以在OUT 端连接一个PMOS 管,其源端接电源,漏端和栅端接在OUT 点,作为一个等效电阻。考虑到图1 中NMOS 管的gm 大小的限制,经过计算取WPL =2μP8μ,其gm = 9. 5μs.负载电容Cl1 和Cl2 取10μ,以确保晶振的振荡频率为32. 768kHz , 在实际仿真中可以对负载电容进行调整以获得准确的振荡频率。Ribias 一般取10M 到25M 之间,当Ribias 增大时,NMOS 管的反相放大器的增益增大,此时振荡器的起振时间变校另外,仿真时为了让电路起振需要在IN 端给一个电流扰动。该部分的仿真结果如图5 所示,IN 和OUT 两端正反馈过程明显,从而产生相位相反的正弦信号。 图5 晶振电路部分IN 和OUT端的电压波形 图4 中要求比较器有较高的增益,带宽超过32. 768kHz ,根据给定的输出最大最小值和传输时间设计好各个管子的宽长比后,仿真得到如图6 所示的比较器的传输曲线。 图6 比较器的传输特性曲线。 由图6 可测得,VOH = 1. 738V ,VOL = 2. 46mV ,失调电压VOS = 21. 28mV. 将图2晶振部分与图4 比较器部分连接后仿真,输出的时钟波形如图7 所示,可以看出其起振时间为625μs ,由于采用的伪电流结构和M5~ M8 的作用,其上升时间仅为0. 017μs , 下降时间仅为0. 008μs.对比用反相器作为整形电路的结构,其起振时间为2ms ,如图8 所示,其最终输出的时钟波形也比用比较器结构的差,例如失真度较高,尽管反相器的管子的宽长比很大,波形的上升时间和下降时间也很长,而且它的低电平部分不能完全到达0V. 图7 晶振整体电路的输出时钟波形 图8 用反相器整形后输出时钟波形。 通过仿真可得,该电路的功耗为2. 4292μW. 综上所述,比较器电路的仿真结果如表1 所示,整个晶振电路的仿真结果如表2 所示。 表1 比较器电路仿真结果。 表2 整个振荡电路仿真结果 4 结束语 提出了一种用于实时时钟RTC 的32. 768kHz 集成晶体振荡电路的实现方法,采用晶振和比较器的结构,文中分别给出了这两部分的具体电路和分析,并使用Hspice 对所设计的电路进行仿真,从而验证了该电路起振时间短,波形稳定,功耗低等特点。

电路 分析 设计 晶振 32 768kHz 实时 时钟 用于 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)