三电平逆变器SVPWM控制的一种新方法

摘要:针对多电平空间矢量脉宽调制(SVPWM)控制中矢量的选择和作用时间的计算占用大量芯片资源的问题,此处以相邻大矢量为基底,通过矩阵变换的方法合成参考电压矢量,避免了复杂的三角函数运算。采用DSP与FPGA结合的方法搭建控制平台,利用FPGA提高系统的实时性。实验结果证明了该方法的可行性。

关键词:逆变器;三电平;空间矢量脉宽调制;矩阵变换

1 引言

中点箝位(NPC)三电平逆变结构以其明显优势在高压大容量逆变系统中得到了广泛的应用与研究。与传统正弦脉宽调制(SPWM)相比,SVP WM具有直流电压利用率高、易于数字化实现、输出波形谐波含量低等优点。

三电平SVPWM控制可直接使用DSP芯片实现,通过对芯片内部硬件模块编程,产生调制脉冲。但该方法耗费大量DSP资源,输出脉冲时序不能严格同步且数量有限,芯片资源限制了逆变器电平数的拓展。文献采用DSP与CPLD组合的实现方法,在一定程度上解决了芯片资源短缺的问题,但控制算法需进行大量三角计算,影响了控制的实时性,限制了其向多电平拓展。

此处利用DSP的数据处理优势和FPGA并行处理的特点,采用16位数据总线与6位地址总线进行通信,实现了DSP统一寻址,并采用简易算法以增强系统实时性。

2 三电平逆变器SVPWM原理

NPC三相三电平逆变器主电路中每相桥臂包含4只功率开关管Vx1~Vx4、反并联在对应功率管上的续流二极管VDx1~VDx4及两只箝位二极管VDx5~VDx6(其中x对应U,V,W三相)。输出相电压与开关管状态间关系如表1所示(2,1,0为输出电平标记)。每相可输出3种电平,三相共有27种状态,对应α,β垂直坐标平面上的27个空间矢量,其中定义α轴与U相重合。

,Ed/3和0。

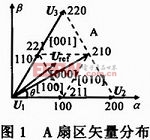

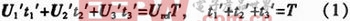

整个平面被大矢量分为A~F6个扇区,各个扇区内部被小矢量与中矢量分成4个正三角形(例如图1中A扇区内[100],[000],[010],[001]),共24个三角形,图1示出A扇区矢量分布图。参考电压矢量Uref由所在三角形的顶点所对应的矢量合成,即最近三矢量法。单位采样周期内任意最近三矢量U1’,U2’和U3’与各自作用时间t1’,t2’和t3’满足下式:

式中:T为采样周期。

3 SVPWM的实现

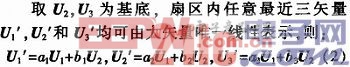

将三电平矢量空间等价为以大矢量与零矢量组成的两电平矢量空间,计算两电平状态下矢量U1,U2,U3作用时间t1,t2,t3;由t1,t2,t3得出小区信息,并对其进行线性变换得出三电平矢量空间下各矢量作用时间,合理安排矢量作用顺序,输出驱动脉冲。

3.1 算法原理

将三电平忽略小矢量及中矢量后等效成两电平,令图1中U1,U2和U3合成Uref,由式(1)可求得作用时间分别为:

3.2 判断小区

令:

λ1=int(2t1/T),λ2=int(2t2/T),λ3=int(2t3/T) (7)

则Uref位于三角形[λ1,λ2,λ3]内,选择该三角形顶点对应的电压矢量合成Uref。

3.3 求解变换矩阵

当λ1+λ2+λ3=1时:

因此,由t1,t2,t3可判断Uref具体位置,并求得对应的变换矩阵,计算得三角形顶点对应三矢量的作用时间t1’,t2’,t3’。

3.4 矢量作用时序

如图1所示,假设λ1=λ2=A3=0,Uref落在A扇区三角形[000]内,Uref由210,211/100,221/110合成,采用五段法,首发正小矢量,顺序为211→210→110→100,然后返回,相电压在采样周期内前后对称,有利于降低输出波形中谐波含量。

4 系统驱动脉冲产生

4.1 硬件设计

FPGA芯片内部为硬件并行执行模式,逻辑资源丰富,接口灵活性及执行速度优于DSP。由FPGA完成矩阵计算功能,可提高系统实时性;DS P芯片在数据采集与分析等功能上较FPGA有独特优势。故控制电路采用DSP与FPGA相结合的方法。将FPGA扩展为DSP的外设。通过16位数据总线与6位地址总线通信,如图2所示。

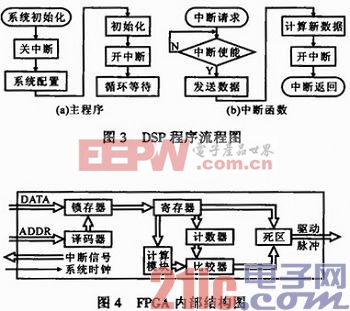

DSP在中断服务程序中将数据发送至FPGA,FPGA经过计算后输出加入死区的高、低电平至驱动电路,驱动功率器件。当主电路故障时,故障信号被送入FPGA,FPGA首先封锁相应驱动脉冲,并向DSP发送故障中断请求。

4.2 软件流程

DSP程序流程及FPGA内部结构分别如图3和图4所示。DSP响应FPGA中断请求后进入中断服务函数。在中断函数中首先向FPGA发送数据,然后计算下一次中断所需数据,以降低程序延时,提高系统的实时性。

FPGA根据DSP发送的数据进行译码,计算矢量作用时间并转换为加入死区的高、低电平输出至驱动电路。当计数器发生周期匹配时向DSP

发出中断请求信号。

5 实验

采用DSP与FPGA建立实验平台,实验参数为:DSP工作频率为100 MHz;FPGA时钟频率为50 MHz;调制度m=0.8;单周期采样数为128次;

死区时间为0.2μs。实验波形如图5所示。

- 实现智能太阳能管理的微型逆变器应运而生(05-06)

- 只需少量器件的廉价自动复位断路器(07-31)

- 即将普及的碳化硅器件(10-19)

- IR2110驱动电路的优化设计(03-15)

- 关键电源及LED照明应用的最新高能效规范要求、设计挑战及解决方案(12-07)

- 基于FPGA的三相PWM发生器(06-23)