低成本多路输出CMOS带隙基准电压源设计

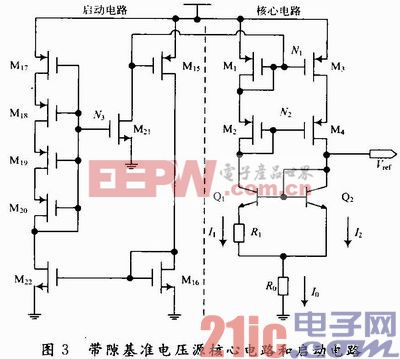

本文所设计的启动电路如图3虚线左侧所示,在电路启动时,N3变为高电位使M21导通,则N1变为低电位使M15导通,并且带隙主电路开始工作,启动完成。由于M16为二极管接法,所以M16支路导通,并且M22与其所在支路也导通了,此时M22的导通将N3拉到较低电位,使M21截止,并且由于M22所在支路的导通,会使M21一直保持截止状态,启动电路停止工作,降低了功耗。

2.3 多路基准电压输出的设计

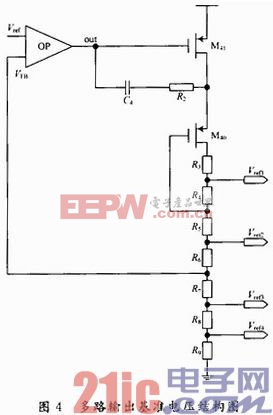

多路输出电路如图4所示,整个电路相当于一个带负反馈的多输出放大器,可以得到稳定的3 V,2 V,1 V和0.15 V基准电压。由于Vref为1.14 V,利用运放的“虚短”可得到Vref1,Vref2,Vref3和Vref4的值,其中Vref2计算式为:

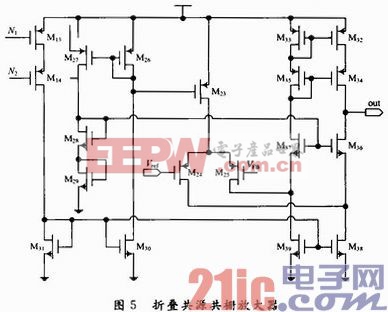

多输出运放的第一级采用折叠共源共栅放大器,如图5所示。

该折叠共源共栅放大器具有宽的共模输入范围和大的输出电压摆幅。同时为了减小共源极失调电压对后级共栅电路的影响,本文在设计过程中使M36和M37支路的电流为M23支路电流的3倍。

在图4中,多输出运放的第二级采用由M41和电阻串组成的共源极电路,提高了增益。C4和R2分别是补偿电容和调零电阻,对整个运放进行频率补偿,增强电路的稳定性。M40的特殊接法是为了降低该管上的压降,从而得到所需的3 V(Vref1)电压。

该多输出运放可以通过选择合适的电阻值,非常方便地得到从0到接近VDD的任意电压值,且这些电压值与电阻的绝对值无关,只与选取电阻的比例有关,因此适用于各种工艺。

3 仿真结果与分析

整体电路采用华虹1μm的CMOS工艺设计,利用Cadence仿真软件进行仿真,并对仿真结果进行了分析。

3.1 带隙基准源仿真结果

带隙基准电压源核心电路的温度特性曲线如图6所示,温漂TCF的计算由下式给出:

由图6可知,在-40~140℃的温度范围内,根据式(11)可得温漂为23.6×10-6℃-1,实现了宽温度范围内低温漂的设计目标;带隙主电路的PSRR为67 dB;静态电流低至24μA,大大降低了芯片的功耗,可以满足开关电源芯片的设计需求。

对启动电路进行瞬态仿真,可以得到启动电路的启动时间为0.114μs,启动速度快,满足设计要求。

3.2 多路输出基准电压仿真结果

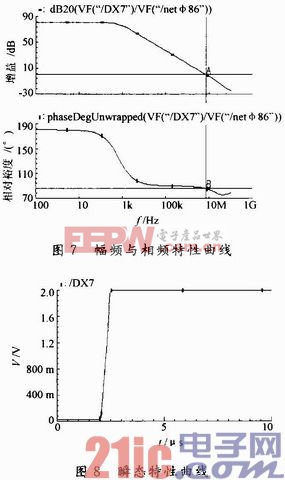

分压电路采用带负反馈的两级运放,跟踪性能好。以Vref2为输出端的仿真结果如图7~图9所示。

对运放的交流小信号增益与相位进行仿真,得到如图7所示曲线。从图中可以看到,运放增益为80 dB,相位裕度为85°,单位增益带宽为7.15 MHz。

对运放进行瞬态仿真,得到图8所示曲线。从图中可以看到,曲线并没有振铃出现,说明运放比较稳定。

根据图8可计算出运放的转换速率为4 V/μs,建立时间为0.58μs。

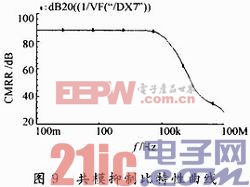

对运放的CMRR(共模抑制比)进行仿真,得到如图9所示曲线。从图中可以看出,CMRR为88 dB,说明运放具有较好的共模抑制特性。

4 结语

结合开关电源管理芯片项目的设计需求,设计了一款多输出、低成本、高性能的CMOS带隙基准电压源。设计中采用了一种结构简单的Brokaw带隙基准核心电路和带负反馈的折叠共源共栅运放,实现了低成本和多输出的设计要求。通过Cadence的仿真结果可以看到,该带隙基准源性能良好,能够提供比较精确稳定的基准电压。

带隙基准源 多路基准电压输出 温度系数 Cadence 相关文章:

- 一种发动机高温差环境下的基准电压源电路(12-24)

- 基于UCC3895与PIC单片机的智能充电器(01-24)

- 基于DC-DC电荷泵的研究与设计(08-20)

- 低压CM0S带隙基准电压源设计(08-20)

- 广泛应用的CMOS带隙基准电压源的设计(11-10)

- TPS54310的平均SPICE模型的建立与应用(11-11)