AD9644:14位串行模数转换器应用详解(原创)

AD9644是一款14位双通道模数转换器(ADC),配有一个高速串行输出接口,采样速度可为80MSPS或155MSPS。这款双通道ADC内核采用多级、差分流水线架构,并集成了输出纠错逻辑。每个ADC均具有宽带宽、差分采样保持模拟输入放大器,支持用户可选的各种输入范围。集成基准电压源可简化设计。占空比稳定器可用来补偿ADC时钟占空比的波动,使转换器保持出色的性能。

控制理论

The AD9644 dual-core analog-to-digital converter (ADC) can be used for diversity reception of signals, in which the ADCs are operating identically on the same carrier but from two separate antennae. The ADCs can also be operated with independent analog inputs. The user can sample any fS/2 frequency segment from dc to 250 MHz, using appropriate low-pass or band-pass filtering at the ADC inputs with little loss in ADC performance.

In nondiversity applications, the AD9644 can be used as a base-band or direct downconversion receiver, in which one ADC is used for I input data, and the other is used for Q input data.

Synchronization capability is provided to allow synchronized timing between multiple devices. Programming and control of the AD9644 are accomplished using a 3-wire SPI-compatible serial interface.

模数转换器结构

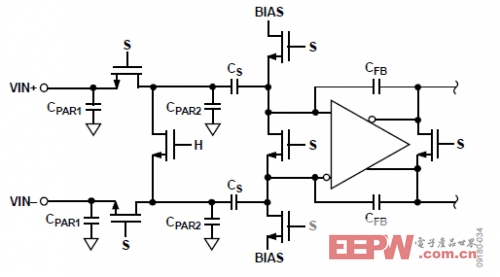

The AD9644 architecture consists of a dual front-end sample-and-hold circuit, followed by a pipelined, switched-capacitor ADC. The quantized outputs from each stage are combined into a final 14-bit result in the digital correction logic. The pipelined architecture permits the first stage to operate on a new input sample and the remaining stages to operate on the preceding samples. Sampling occurs on the rising edge of the clock.

Each stage of the pipeline, excluding the last, consists of a low resolution flash ADC connected to a switched-capacitor digital-to-analog converter (DAC) and an interstage residue amplifier (MDAC). The MDAC magnifies the difference between the recon-structed DAC output and the flash input for the next stage in the pipeline. One bit of redundancy is used in each stage to facilitate digital correction of flash errors. The last stage simply consists of a flash ADC.

The input stage of each channel contains a differential sampling circuit that can be ac- or dc-coupled in differential or single-ended modes. The output staging block aligns the data, corrects errors, and passes the data to the output buffers. The output buffers are powered from a separate supply, allowing digital output noise to be separated from the analog core. During power-down, the output buffers go into a high impedance state.

模拟输入注意事项

The analog input to the AD9644 is a differential switched-capacitor circuit that has been designed for optimum performance while processing a differential input signal.

The clock signal alternatively switches the input between sample mode and hold mode (see Figure 1). When the input is switched into sample mode, the signal source must be capable of charging the sample capacitors and settling within ½ of a clock cycle.

Figure 1

A small resistor in series with each input can help reduce the peak transient current required from the output stage of the driving source. A shunt capacitor can be placed across the inputs to provide dynamic charging currents. This passive network creates a low-pass filter at the ADC input; therefore, the precise values are dependent on the application.

In intermediate frequency (IF) undersampling applications, any shunt capacitors or series resistors should be reduced since the input sample capacitor is unbuffered. In combination with the driving source impedance, the shunt capacitors limit the inp

AD9644 相关文章:

- AD9644:14位串行模数转换器入门必读资料(独家)(11-11)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)