集成电源噪声抑制的时钟源简化FPGA系统的电源设计

1 引言

就本质而言,FPGA是一种耗电设备,需要复杂的电能传输和多电压轨。单芯片通常有数瓦功耗,运行在1.8V、2.5V和3.3V电压轨。激活的高速片上串行解串器(sERDEs)会增加几瓦功耗,并且使电能输送策略复杂化。当FPGA功耗增加时,对敏感的模拟和混合信号子系统性能的要求也随之增加。其中最重要的是时钟子系统,它们为FPGA和其他板级元件提供低抖动的时钟参考。

2降低电源噪声,提高转换效率的通用方法

耗电系统无法避免电源噪声。

一般而言,系统设计者应尽可能的尝试使用低噪声线性电源。然而,过高的管耗通常阻止了线性稳压器的应用。当使用线性设备时,如果不计负载电流,调节3.3V输入到1.8V输出的转换效率仅有54%.低转换效率把电能消耗在稳压器而不是负载上,使线性设备无法满足许多高性能应用的要求。

2 LDo的优缺点

通过减少调节过程中输入到输出的电压差,低压差线性稳压器(LDO)的应用有助于提高转换效率。例如,2.5V到1.8V调节可为全部负载提供高达72%的转换效率。

这在负载所需电流不超过500mA时,通常是一个好的做法。然而,当负载需要lA~3A的电流消耗时,LDO就不能提供太大的帮助了。当稳压器处于输入输出电压差范围之内时,它不能再进行有效的调节。

其外在表现就像一个电阻器,无法响应负载电流或输入电压的变化。

结果削弱了稳压器的噪声抑制能力,不适合为敏感电路模块供电。

为了保持良好的调节和噪声抑制能力,LDO必须使用比它们输入输出电压差规范中规定的更高的输入电压供电,这降低了转换效率。为满足输入输出电压差的条件要求,多个LDO可并联在一起,以减少通过每个稳压器的负载电流。但是,复杂的结构和高昂的成本使得这个替代方案没有什么吸引力。

3 开关稳压器的优缺点

提高转换效率和维持宽负载电流范围调节的更实际的方法是使用开关稳压器。开关稳压器有高达85%一95%的转换效率,这常常使其成为FPGA的唯一选择。随着效率的提升,伴随而来的副作用是多达50mVp-p“100mVp-p的电压纹波噪声。由于FPGA逻辑和I/O电路的高功耗,导致通常低于50mV.的开关纹波要求是高成本和不切实际的。

4 其它噪声和挑战

另一种噪声来源是FPGA本身。结构内系统时钟可能运行在数十到数百兆赫兹。当高功率数字逻辑运行时,其产生的噪声瞬变波及到各种电源层。快速瞬变产生高能量毛刺,需要电源滤波器进行平滑处理。由于大多数电源去耦优化仅仅在一个或几个频率上呈现低阻抗,因此很难甚至不可能清除所有电源轨上的高频噪声。噪声会通过电源传播到其他子系统,特别是那些靠近FPGA的子系统。 FPGA面临着另~个挑战。当逻辑或I/O电路在低和高功率运行状态之间切换时,负载电流显着波动。当逻辑电路进入集中运行的高功率运行状态,电源的负载加重。

当逻辑电路进入低功耗状态,负载减轻,电源返回正常状态。许多活动能够产生这种负载变化,而且这些活动的变化规律一般是无法预测或控制的。负载变化在电源轨上产生低频包络,一般低于100kHz.

噪声包络可以使用额外的稳压器清除,但是增加了成本和电路板空间,减少了电源设备的利润。

由于这些原因,当与FPGA共用同一电源轨时,敏感模拟组件面临着考验。在许多情况下,用户可能会遇到莫名其妙的性能下降或异常等不可预知的行为。传统的解决办法是每个敏感时钟系统使用隔离的电源供电,这些电源使用线性稳压器来过滤低频噪声,使用大量的由磁珠和陶瓷去耦电容组成的LC过滤高频噪声。然而,这不是一个理想的解决方案,因为它增加了成本和设计复杂度。此外。它割裂了电源层,在提供低阻抗和可靠耦合的回路方面降低了性能。更好的解决办法是保持一个连续的电源层,整个板上尽可能的完整。然而,为了利用这一优势,每个子系统必须能够承受电源噪声。

5 FPGA对时钟源的特殊要求

当前,FPGA严重依赖低抖动时钟源,以满足终端应用需求。

FPGA可驱动背板、光学模块,或GMII/xGMlI接口,所有这些都需要超低抖动的时间参考。如何运行在FPGA弓I起的嘈杂环境中,已成为FPGA参考时钟设计面I临的主要挑战。

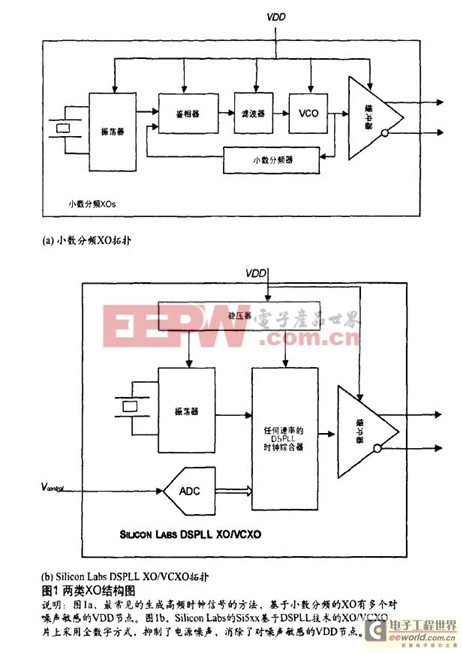

图la和 图lb所示为两种类型的XO结构图。晶体已经被使用f数十年来作为大多数电子系统的脉搏。他们为多种高性能应用提供了低相位噪声、良好的频率精度。以及足够的性能。尽管有这些优点,晶体还是有一个主要的限制:基频振荡要低于50MHz.对于大多数高性能应用,晶体必须配合一个PLL,用其倍乘低频参考,从而产生需要的输出频率。PLL常用于对一个初始频率进行倍乘,可以是一个整数值(例如3)或小数值(例如3.125)。

图1(a)的小数分频拓扑图是由一个

- 一种高度集成的全新电源管理解决方案(12-09)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)