基于AD9650的高速数据采集系统的设计方案

程,这个卷积过程在整个频谱域有效,同时在微观上也同样有效。因而,图2所示的时钟频率周围集中的相位噪声也将与模拟输入进行卷积,造成输出的数字信号频谱失真。

采样时钟相位噪声通常以单边带相位噪声来衡量,即:

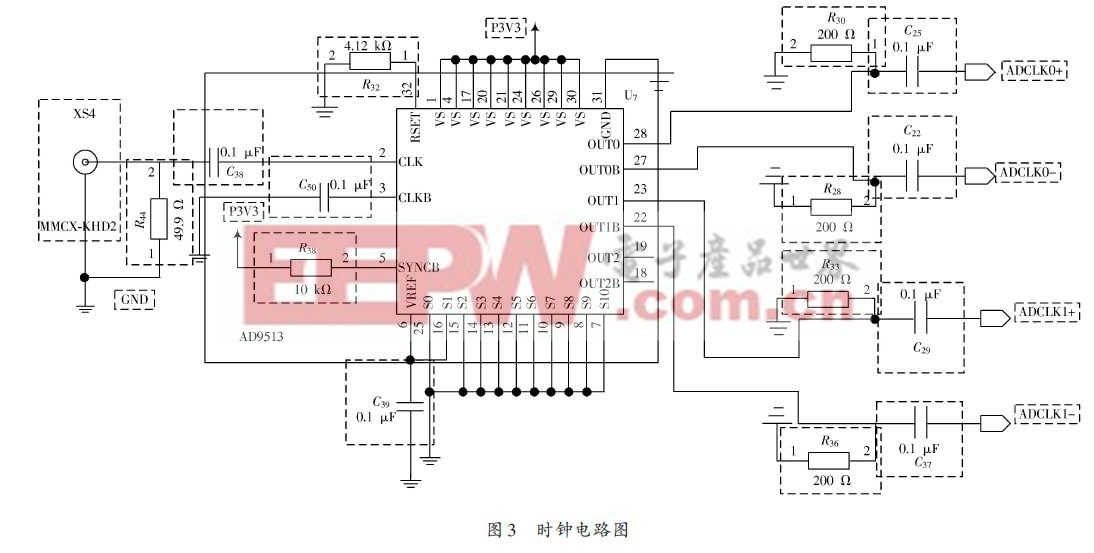

由此可以计算出采样时钟相位噪声,作为系统设计的依据。在本系统中,为保证时钟特性,时钟源由高精度晶振提供,时钟抖动控制在1.2 ps RMS以内,相位基底噪声为-165 dBc/Hz.板上时钟转换选用AD 公司的AD9513,其附加的时钟抖动为300 fs,输出的时钟信号性能满足要求。它实现对单路时钟转两路LVDS信号,给AD9650 提供采样时钟,同时给FPGA 提供同步控制时钟。图3给出了时钟电路设计原理图。

2.3 前端电路设计

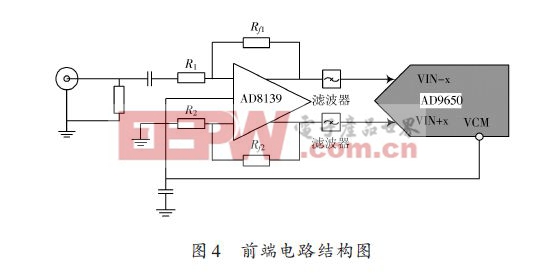

ADC前端电路主要完成对模拟输入幅度、信号形式的调整。它采用交流耦合方式,通过差分放大器,实现对信号幅度调整,同时实现单端输入信号转差分信号。并且,通过后续的滤波器实现信号的滤波。其结构如图4所示。

虽然差分运放是有源器件,使用中会消耗功率,且产生噪声,但它的性能限制比变压器少,可以在必须保留直流电平时应用,而且放大器增益设置简单灵活,且通带范围内提供平坦的响应,而没有由于变压器寄生交互作用引起的纹波。

ADC的 S (N + D) (信号噪声失真比)是决定驱动放大器的关键因素。如果在目标频率范围内,驱动放大器的THD ( 总谐波失真加性噪声) 总是优于ADC 的S (N + D) 值 6~10 dB,那 么 所 有 由 放 大 器 造 成 的S (N + D)降低将相应限制在接近0.5~1 dB.

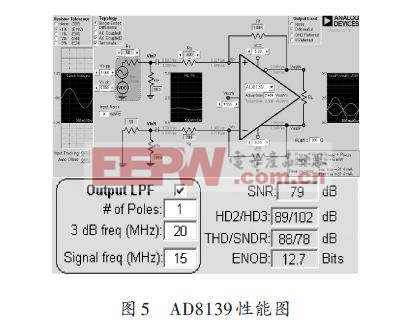

利用ADI 公司提供的ADI DiffAmp Calculator 软件可得到前端电路仿真图,如图5所示。由文献[3]可知在输入信号为15 MHz时,AD9650的 S (N + D) 为82 dB,而图5 中AD8139 的THD 为88 dB,满足上述要求。综合考虑增益及通带内响应及输入阻抗等因素,前端电路采用ADI公司的差分运放AD8139.

3 方案设计系统结构及实物

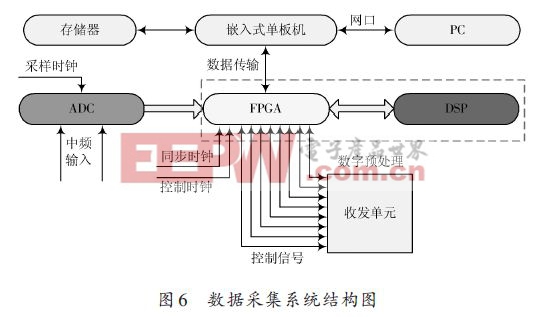

根据系统要求,设计的高速大动态范围ADC 数据采集系统,结构如图6所示,主要包括模数转换模块、数字信号预处理模块、数据传输模块和嵌入式单板机等。

模数转换模块是信号采集系统最重要的组成部分。它主要包括ADC、前端电路和时钟电路等。主要完成的功能是实现对模拟中频输入信号的数字化,以用于后续的数字信号处理。

数字信号预处理模块采用较为成熟的FPGA+DSP结构,主要实现对数字信号的FFT、数字正交解调等,同时实现对原始数据传输。信号预处理主要在DSP中完成,而FPGA内部搭建两个FIFO来实现数据传输,同时完成对收发单元等的控制功能。FPGA采用Xilinx的低功耗高性能产品Spartan6,DSP 采用Analog Device公司的低功耗DSP产品ADSP21479.

数据传输模块采用Cypress 公司的CY7C68014,通过USB 接口完成由FPGA 向嵌入式单板机的数据传输。嵌入式单板机具备各种符合计算机协议的数据接口,包括与电子硬盘的存储接口,与上位机的网络通信接口,以及与预处理卡的USB通信接口。

数据采集系统硬件电路实物,如图7所示。系统分成两块电路板,即模拟ADC板和FPGA+DSP数字板,两者通过PMC插件连接。

4 结语

本文研究了影响数据采集系统动态范围的关键因素,给出了在采集系统设计时选择芯片、设计时钟和前端电路的依据,以此为基础提出了一种高速数据采集系统的设计方案。论证分析表明,该设计方案能够满足雷达数据采集系统高速大动态范围的要求。

- AT84AD001型ADC在高速信号采集系统中的应用(01-21)

- 基于LPC2103的三相电信号数据采集系统的设计方案(12-13)

- 完整的5V单电源8通道多路复用数据采集系统(08-03)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)