FPGA+DSP协同平台设计之调试技巧和注意事项

1 FPGA和DSP的隔离调试技术

作为双芯片的协同系统,调试的开始阶段需要对每个芯片进行单独测试。这种情况下就需要避免另外一个芯片对调试产生影响,比较好的办法就是让它停止工作。

对于FPGA芯片,如果没有进行配置,那么所有的管脚都处于高阻状态。由于高阻态没有驱动能力,所以不会对DSP产生直接的影响。但是在某些情况下,会产生间接的影响。

例如,很多DSP会在系统复位的时候读取某些地址信号来确定启动后的工作模式。如果这些信号连接到了FPGA的管脚上,那么上电后这些信号就会处于不确定的状态。如果处于错误的电平状态,就会对DSP产生很大的影响。

解决的办法就是通过上拉或者下拉电阻来保证这些处于高阻态的信号处于正常的状态,如图11.10所示。这样,在FPGA的管脚处于高阻状态的时候,管脚会被上拉到高电平或者下拉到低电平。

图1 双端口RAM模块

DSP芯片和FPGA芯片不同,即使在没有进行配置的情况下,有些管脚也会处于输出状态,比如地址信号和控制信号。那么在单独调试FPGA芯片的时候,就要考虑到这些管脚是否会对FPGA产生影响。

特别是没有用到(unused)的FPGA管脚,有些系统默认的状态是低电平。这些管脚如果和DSP的输出管脚连接到一起,就会出现总线的冲突情况。因此,在工程项目设置的时候,要将UNUSED PIN指定为高阻态或者INPUT模式。2 FPGA测试点的设计

FPGA芯片的管脚资源一般都很丰富,除了满足系统应用外,还会剩余部分管脚没有指定功能。这些剩余的管脚用来做测试点会方便系统的调试。

例如,DSP的地址和数据信号都属于高速信号,如果直接在这些信号上加测试点测试会影响到信号的波形质量。特别是BGA封装的DSP芯片,这些管脚不能用示波器设备的探头或表笔直接测量。而且,板上的测试点太多也会影响布线的质量和美观。

充分利用FPGA的灵活性,可以将需要测试的信号指定到某个测试点上。这样就不需要直接测试这些信号点,而是通过测试点进行间接的测量。

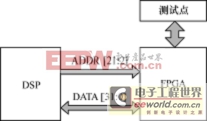

如图2所示,如果需要测试DSP的信号ADDR[15]和DATA[0],可以把这两个信号在FPGA内部指定到测试点T1、T2。只要直接测试T1、T2就可以了。

此外,这些测试点还可以用来做功能扩展。因为这些测试点都是双向的普通I/O,可以作为连接器信号和其他板卡或者系统互联。

3 借助FPGA的内部逻辑分析仪来辅助调试

在前面的章节中曾经介绍过FPGA的内部逻辑分析仪功能,如Altera公司的Signal TAPII和Xilinx公司的Chip Scope等。这些工具可以用来测试FPGA运行状态下信号的变化情况,特别是总线的运行状态。

在FPGA+DSP的系统中,DSP的很多信号需要连接到FPGA的管脚。利用内部逻辑分析仪功能,就可以通过FPGA来观察这些信号的时序和状态,提高了调试的可视化程度。

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 适合高效能模拟应用的线性电压稳压器(07-19)

- TPS54350在信号处理系统中的应用(06-09)

- 基于FPGA的三相PWM发生器(06-23)

- 嵌入式 POL DC/DC 转换器设计(07-22)

- 电源管理与转换的整合可简化电源系统设计(07-24)