AT84AD001型ADC在高速信号采集系统中的应用

据在同一相位输出,有利于接收系统进行同步数据读龋5 系统设计

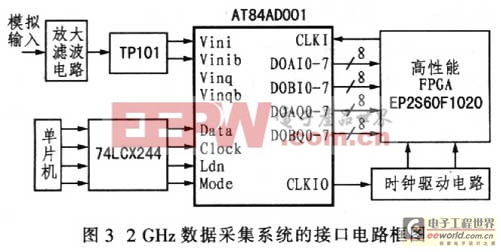

AT84AD001在图2所示的工作时序下,输出4路8 bit-500MS/s LVDS逻辑的数据,在采集系统设计中对与其接口器件的性能要求也较高。Altera公司的Stratix2系列FPGA-EP2S60F1020具有高达84个专用LVDS差分逻辑接收通道,每个LVDS通道数据传输速率最高达640 MS/s。一片EP2S60F1020即可满足接收ADC输出数据和逻辑控制的需要。由于ADC的输出和FPGA的输入均设计为LVDS逻辑标准,因此,ADC可直接与FPGA相连。Stratix2系列FPCA内部具有专门的LVDS处理单元,可实现LVDS逻辑的串/并降速转换,降低速率后的数据可提供给内部DSP处理单元进行处理。Stratix2系列FPGA的另外一个优点是其内部具有专门的高速数字锁相环电路,能够产生可供ADC电路使用的时钟信号。

图3所示为基于AT84AD001的2GHz数据采集系统的接口电路框图。模拟输入信号经过前置放大滤波电路,再经过一个射频变压器TP101将单端信号转换为差分信号,送入AT84AD001的I通道模拟输入端,由于所选的特殊的工作方式,Q通道的模拟输入端无须输入信号。ADC的工作时钟CLKI由FPGA提供,FPGA输入一个频率较低的时钟,经内部数字PLL倍频和逻辑组合产生频率为1GHz的工作时钟,作为ADC的采样时钟CLKI。在图2所示的工作模式下,ADC的数据准备信号CLKIO可以作为系统数据采集和处理的同步时钟,CLKIO为差分LVDS逻辑,速率为250MS/s,在时钟的上升沿和下降沿均起作用。ADC输出4路8bit-500MS/s的数据,共占用FPGA的32个LVDS逻辑输入通道。ADC的三线串行接口通过一个AVR系列单片机ATmegal28L进行控制,其中单片机产生的信号逻辑电压为3.3V,而ADC三线接口逻辑电压为2.25V,因此需要在单片机和ADC之间加一个缓冲器74LCX244进行电平转换。

6 结束语

介绍了采用高速BiCMOS技术的AT84AD001型模数转换器,并将其应用在2 GHz数字采集系统中。它的典型三线串口功能简化了ADC的外围电路设计,提高了超高速电路的性能。由AT84AD001及其接口器件EP2S60F1020构成的数据采集系统采样速率达到了2GS/s,可以应用在现代宽带通信中。随着现代超宽带技术的发展,这种超高速数据采集方案可以用来设计一种全数字化超宽带(UWB)接收器的数据采集系统,以便将软件无线电技术应用于超宽带通信系统中,而高速ADC在全数字化超宽带接收器的设计中起了关键作用。

AT84AD001型 ADC 高速信号采集系统 相关文章:

- S3C2440A嵌入式手持终端电源管理系统设计(01-11)

- 基于CAN通信的电源监控系统的设计(04-06)

- 基于MSP430单片机的电源监控管理系统(04-20)

- 适用于全球交流电源的单节锂离子电池充电器设计(06-07)

- GPIB芯片TNT4882在多路程控电源中的应用(06-08)

- AD7656的原理及在继电保护产品中的应用(06-18)