一种带失调自校正运放的电流采样电路设计

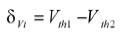

电压[5]:

(1)

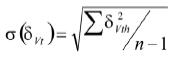

(1)

(2)

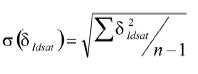

(2)

(3)

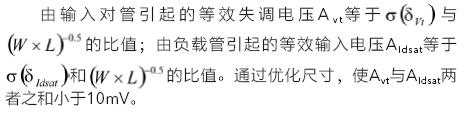

(3)

(4)

(4)

如图2所示,为了能够使运放失调得到校正,在其中一条负载管MP2支路上并联一些小尺寸的管子,来引入失调,通过trim位步进的调整,使输入失调慢慢减少到0。

3 结果分析

图3给出了本文的功能性仿真示意图,可以看出,刚启动时,运放输入两端的等效失调电压为9mV,通过时钟控制计数器使trim位b[4:0]每周期跳变一位,使输入端的失调电压慢慢减小,失调电压接近0时,通过镜像使失调电流到电阻R2上,其上的压降Vimon也慢慢减少,当Vimon接近0的时候,比较器输出端ZCD变高,校正标志位Cal_done变高,校正结束。

采用本电路结构的电流采样电路已经成功应用于数款电源管理芯片中,量产测试结果表明,其电流采样精度小于0.2%。

4 结论

本文首先分析了运放失调产生的原因,随后给出了适合在电源管理芯片中带失调自校正运放的电流采样电路的设计,之后分析了电路工作原理和失调计算方法。该电路结构设计简单,无需开关电容相关技术,可节省一定的芯片面积,同时可使失调电压降到可控范围内,非常适合大规模工程应用;之后给出的仿真结果图,使电路工作过程一目了然。采用该结构的电源管理芯片,量产测试结果表明,其电流采样精度小于0.2%。

参考文献:

[1王松林,张树春,叶强,等.一种采用改进自调零技术的误差放大器设计[J].复旦学报, 2010, 49(6): 667-673.

[2]贾子涵,冯全源,庄圣贤. 适用于DC-DC开关电源的振荡器设计[J].电子元件与材料, 2015, 34(3): 29-32.

[3]苏丹,胡永贵,徐辉.一种同步降压型DC-DC转换器驱动电路设计[J].微电子学, 2014, 44(6): 709-712.

[4]LEE C F, MOK P K T. A monolithic current-mode CMOS DC-DC converter with on-chip current-sensing technique[J].IEEE JSSC, 2004,39(1):3-14

[5]Behzad Razavi. Design of analog CMOS integrated circuits[M]. Boston: McGraw-Hill, 2001:376-389.

本文来源于中国科技核心期刊《电子产品世界》2016年第7期第65页,欢迎您写论文时引用,并注明出处。

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 高效地驱动LED(04-23)

- 电源SOC:或许好用的“疯狂”创意(07-24)

- 实现智能太阳能管理的微型逆变器应运而生(05-06)