针对单纯数字逻辑型电路板ATE设备的设计

电子装备在海军舰艇上应用广泛,如观通、导航、指挥控制、电子战和武器控制等,属于舰艇关键设备,开关电源模块电子装备以其智能化、小型化、高速、高复杂度的特点,在大幅度提高舰艇生命力和作战效能的前提下,也为舰艇维修保障部门和人员带来了巨大的挑战。随着部队MTD2002信息化建设的不断普及与深入,武器装备的维修保障技术正在发生新的变化口_引:自动测试系统及设备ATE(Automatic Test Equipment)、便携式维修辅助PMA(Portable Maintenance Aids)、交互式电子技术手册IETM(Interactive Electronic Technical Manual)等已经成为MTD2002武器装备维修领域的研究热点。ATE是以计算机为基础的故障诊断技术设备,投入使用后,加速了测试过程,提高了维修速度,还可以预防未发生的故障,进而提高装备的质量和性能。舰艇电子装备中的开关电源模块电路板存在多种类型,这里仅考虑针对单纯的数字逻辑型电路板ATE设备的设计。

2 系统总体设计

测试单纯的数字逻辑型电路板,首先需要找出电路板接口引脚上的信号特性,如开关电源模块信号电平(TTL型、CMOS型等)、信号方向(输入、输出或双向)、信号功能(电源信号、逻辑信号),在此基础上通过电路原理图分析电路板功能,设计测试向量,以确定响应向量。信号特性及电路原理图的获取有以下途径:(1)由电路板研制设计单位提供;(2)使用测量仪表手工测绘。

ATE测试的原理就是向电路板输入测试向量,获取相应的输出向量,将此MTD2002输出向量与正常的响应向量相比较,结果一致表明开关电源模块电路板无故障,否则表明该电路板已损坏。整个过程由ATE自动完成,因此效率高,但测试向量的完备与否对故障诊断结果有重要影响。该ATE设备是针对某电子装备系统而研发的,其结构框图如图1所示。

从图1可见,ATE由信号发生、信号采集、与上位机的USB通信以及用于连接被测板的接插件4大模块组成。开关电源模块信号发生模块和信号采集模块采用单片机AT89S51+FPGA的技术方案实现,因此整个测试系统是一个PC机→单片机→FPGA→被测板的4级结构。USB通信模块选用USB/RS-232转换器实现,AT89S51串口经电平转换电路转换为RS-232接口后连接到USB/RS-232转换器。接插件模块主要考虑与被测板连接的电气与机械特性。

3 关键模块设计

3.1 信号发生模块设计

该模块由单片机控制桥(AT89S51)、测试向量存储器(静态存储器HM628128x2,排列方式为256 Kx8 bit)、开关电源模块信号发生FPGA(Altera公司Cyclone系列PLD器件EP1C3)、通道控制CPLD(Altera公司MAX7000系列PLD器件EPM7128S)及三态选通门阵列(74LS126x16)组成,模块组成结构如图2所示。

单片机控制桥收到上位PC机传来的测试向量后,将其写入测试向量存储器(单片机内的存储器不够用),并将被测电路板的引脚信号特性数据写入通道控制CPLD。由CPLD控制三态门阵列的选通端,三态门阵列的输入数据由信号发生FP-GA提供,FPGA接收到控制桥的信号发生命令后,从测试向量存储器取出测试向量送往三态门阵列。控制桥重用FPGA访问测试向量存储器的总线,为防止两者对存储器的访问冲突,用信号Ctrl0和Ctrl1进行开关控制,当Ctrl0=0且Ctrl1=0时,控制桥掌控存储器的访问总线,否则由FPGA掌控。

这里要解决的关键问题之一是自动配线问题。由于各块电路板的输入输出引脚不固定,自动配线除了保证MTD2002信号送达被测板相应的输入通道外,需要避免信号发生模块将信号输出到被测电路板的输出通道,以防止损坏被测板。设计中该问题通过三态门的高阻态得以解决。

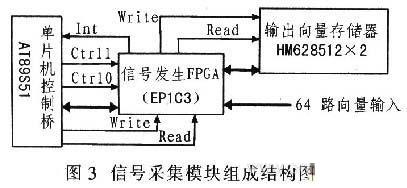

3.2 信号采集模块设计

由于被测板是单纯的数字逻辑电路,电路板的输出信号是数字信号,因此信号采集时无须A/D转换,只需按照一定的开关电源模块采样周期采集输出信号即可。由于单片机数据输入口的位宽一般仅为8位,为了保证采样速度,利用FPGA器件的内在并行性快速采集输出信号,并存入存储器中,在到达测试深度后,FPGA向单片机发送中断请求,单片机从存储器中读取采集到的输出信号,通过USB传送到上位PC机。该模块组成结构如图3所示。

与信号发生模块类似,单片机控制桥重用FPGA访问输出向量存储器的总线,为了避免总线访问冲突,开关电源模块控制桥利用控制信号Ctrl0和Ctrl1,当Ctrl0=0,Ctrl1=0时,控制桥掌控访问存储器的总线,否则由FPGA掌握该总线。

与信号发生模块类似,单片机控制桥重用FPGA访问输出向量存储器的总线,为了避免总线访问冲突,开关电源模块控制桥利用控制信号Ctrl0和Ctrl1,当Ctrl0=0,Ctrl1=0时,控制桥掌控访问存储器的总线,否则由FPGA掌握该总线。

4 系统工作原理

4.1 系统工作过程

ATE测试的基本原理:向被测板输入测试信号,然后获取被测板的输出信号,并与响应信号相比较,依据两者是否完全一致,判断被测板有无故障。ATE工作过程如下:

(1

单纯数字逻辑型电路 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)